|

- Zmake |

|

- Test on Runtime - The inspector tool |

SPE Single Pair Ethernet 10Baset-T1L for fast step times 50 µs

|

SpeA-Videos Some videos to show usage and approaches SpeA-Manual description SpeA-ControllerSw description SpeA-Board description SpeA-FPGA functions and description |

It is a simple connection for field communication, it can be become a really common standard

for field busses till the end points of control (measurements and actuators), including power supply over data line.

|

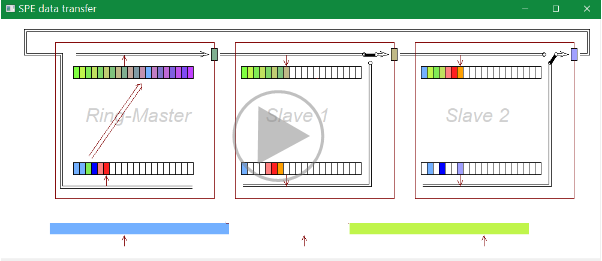

Ring topology

For long distances: 10 Mbit/s, though fast cycle till 50 µs

|

Cycle time synchronization

Dedicated delay and less jitter between receive and forward transmit

in the ring or for switches, the SFD is the synchronization point. SFD = "Start Frame Delimiter", left cursor is on SFD of the blue channel, right on red. The Sync-Phase in the telegram is used to synchronize the clocks in all stations. . |

|

An evaluation board with FPGA and SPI access to controller