1. Approach

This card is an evaluation board to transfer data via Single Pair Ethernet (SPE) with correct physical layer but with a maybe modified OSI Layer 2 and above (depending on software too) to communicate in a Ring topology for a fast cycle time down to 50 µs using the standard 10 MBit/s data rate.

This card can adapt to any controller via SPI interface, both with 3.3 V and also 5 V connections. The controller should support SPI with 10 MBit/s and DMA for elaborately fast data. If this controller in a ring should only use slow data, it can be have a lesser SPI connection without DMA.

2. Operation modes,

2.1. SPE-ring topology fast data transfer

The SpeA card is firstly recommended to use in a Ring topology for specific stations without using a switch for fast data transfer with the data on the fly principle. It gets its data immediately before transmission on SPE from the RAM of the controller via SPI access (Serial Peripheral Interface) and it writes received data immediately after receiving via SPI to the RAM of the controller. The controller can prepare the data just in time before transmission and immediately after receive to get a small as possible delay of the whole signal processing (less dead time in a controlling loop). That is the main approach of usage. For that the SpeA-card and the controller should be prepared by programming of course.

If the SpeA-card is Master in a Ring, it expected the echo of the telegram in the ring in a deterministic time. But the delay depends on the number of stations in the ring and the delays in the cable. The receiving data are synchronized with the transmission data to read and write one word via SPI simultaneously. The correspond received word is at least one 16 bit delayed, of course, maybe more as 16 bit steps on longer delays.

2.2. SPE ring topology fast data in ring but slow access from the controller

This mode is intended for a controller as station in the ring which is not enough powerful for fast SPI access with DMA. It means the data cannot be fast transferred from and to the RAM via SPI. The station should be a slave in the SPE-Ring. It means it forwards received data to the transmitter without the controller. Only a few data words are stored in the FPGA from the received telegram and read from a FPGA-register to replace few data words in the forward transmitted telegram. The controller can access this registers via SPI in a slow way.

2.3. SPE ring topology for extensive data with PC in ring

This mode allows the immediately connection to a PC net in context of data exchange between controller with a high time accuracy. The cycle time for the data exchange can be 1..2 ms due to the transfer rate of 10 Mbit/s and a telegram length of 800..1500 Byte. 1 till 2 milliseconds is a proper value for synchronized mechanical movements, but also for fast second level electrical control.

It is necessary to use an extra Ethernet card on the PC for this approach, because this Slot should transfer with 10 Mbit/s full duplex. The integration in a local PC net is possible, if the router transfer the data after the immediately 10 Mbit/s plug with an higher speed, it means a special router should realize the 10 Mbit/s baud rate.

2.4. SPE star or multidrop data transfer, extensive data

For this operation mode only one connection is intended to use. The SpeA card and the controller should be programmed normally as SPE-slave, the SPI should be prepared. The received data from a telegram are written in the RAM of the controller via fast SPI access. After the telegram an interrupt should be triggered which tests the data. If the data are proper for an answer, the SpeA-card and the controller should be programmed one time as SPE-master, transmit the answer (the line should be in gap state before), and after transmission immediately the card should be programmed again as SPE-slave for receiving. For this operation mode the controller should be fast act for this network data transfer. It is not the best divide solution for evaluation the data on PHY chip level.

If the SpeA-card with the FPGA works in Star or Bus Topology or as Master in Ring topology, then it is always Master.

The time of the telegram is determined by the controller, which initializes the SPI

for the data transfer and outputs the frame_in signal to start the telegram.

2.5. SPE star or multidrop data transfer, less data

This is similar as the mode before. The difference is, the data are stored in the FPGA. Maybe also answer data can be stored and automatically answered (depending on the content of the FPGA). The received data and answer data can be read and written in a slow cycle via SPI access from the controller as master. This mode is intended to use for a less powerful controller as station.

Another possibility of usage is: The SpeA-card is a participant on a multi drop line or it is connected to a switch. It is prepared to receive data. The data will be written immediately to the RAM of the controller.

2.6. Default mode: SPE Ring topology slave

A SpeA-card which is not connected to the controller, or the controller is in reset or crashed after reset, the SpeA-card should act as SPE-Ring Slave. This is important because the communication in the Ring should not depend on the proper work of any station in the ring. On faulty the ring should primary work.

Only the dedicated master in the ring can be determined by hardware to prevent this SPE-Ring Slave forward transmission. This is necessary because otherwise a life of its own can occur: A telegram can be generated and circle continuously in the ring. The master functionality breaks this forward transportation, and the ring is silent if the master is silent.

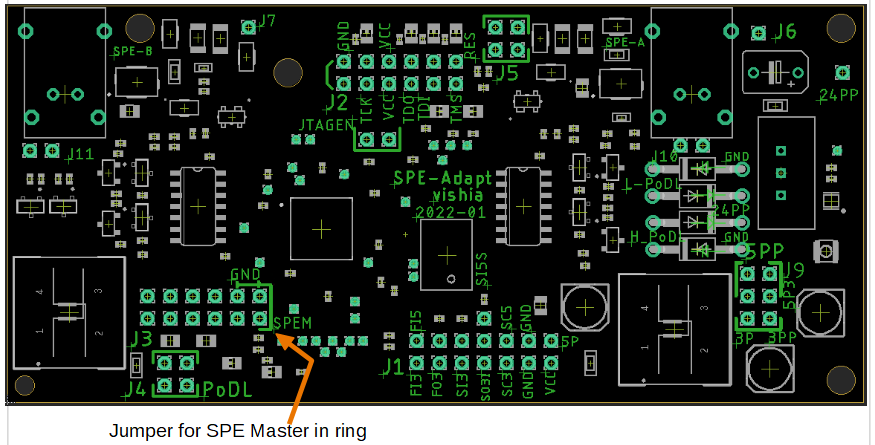

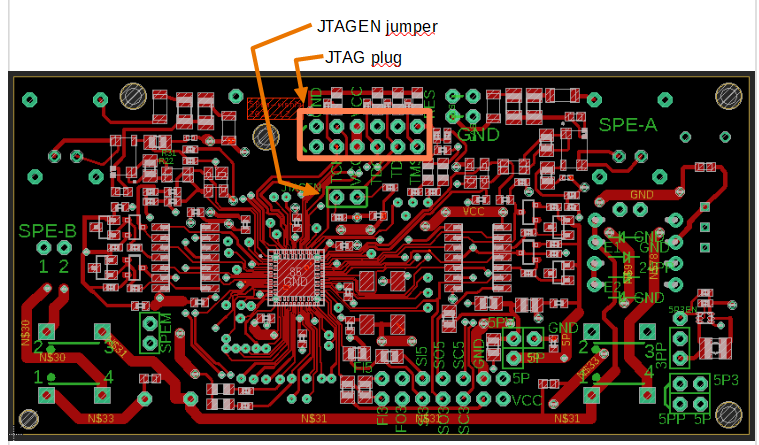

The hardware determination for master is a jumper (connection) between J3.9 (FPGA pin A16) and J3.10 (GND).

2.7. Set the configuration with SPI master access from controller

Without using the frame_in signal, held it inactive low, the SPEa-card can be accessed for all configuration and data register via SPI,

whereby the controller is master of SPI, the SpeA-card is slave.

3. Physical (electrical) Interface to the controller card

3.1. Pin header on the adapter card

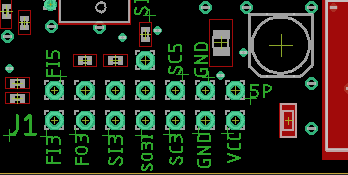

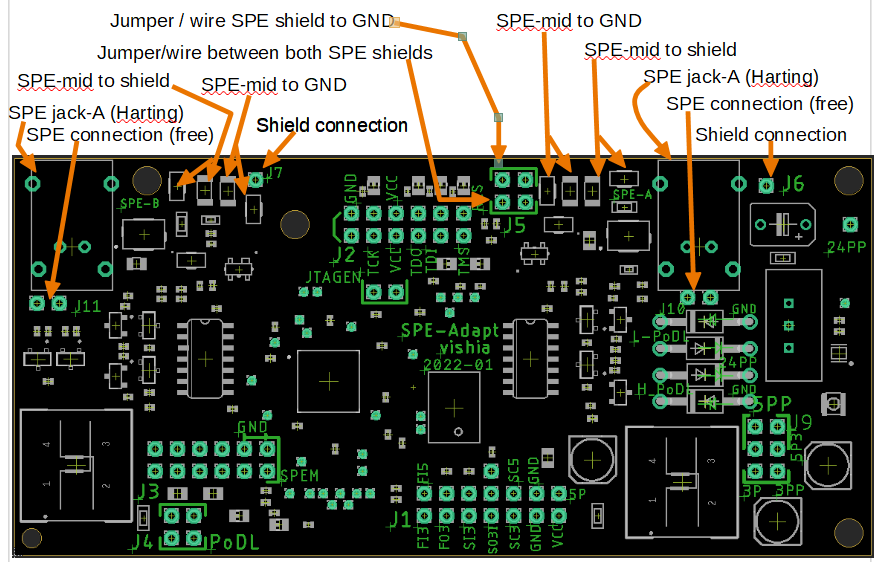

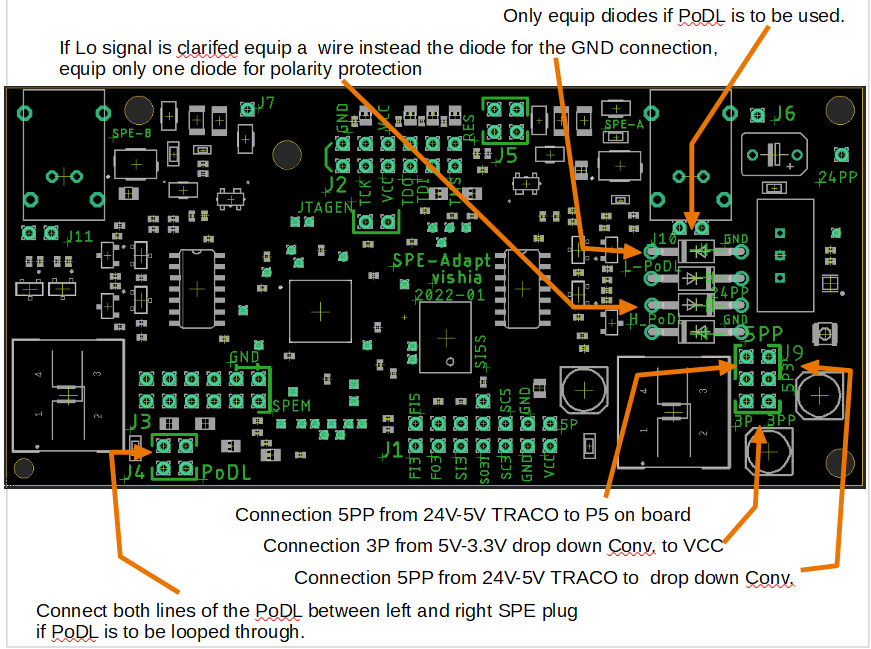

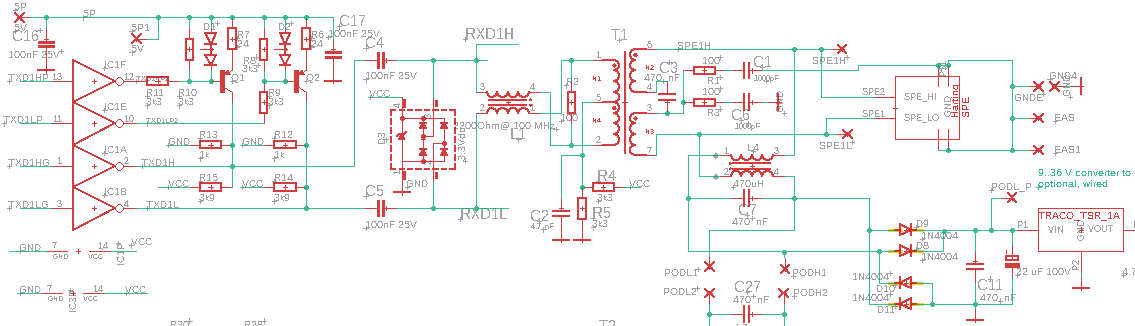

You see here soldering points which can be also a pin-header for Power supply, SPI, and the Frame signals.

Right side you have a VCC (3.3 V) plug, and above the adequate 5P plug for 5 V. Left of that there are two ground plugs. Then to the left, the lower raw contains the 3.3 V pins, which are immediately connected to the FPGA pins. The pins exactly above are the correspond pins for 5 V level. There is one pin outside. This is a second input for SPI if the SPE-Adapter card is SPI-Slave as MOSI with 5 V level.

SI5S

x

FI5 FO5 SI5 SO5 SC5 GND 5P

x x x x x x x

x x x x x x x

FI3 FO3 SI3 SO3I SC3 GND VCC

3.2. 5 V or 3.3 V interface

Some controller have a logic level of 5 V due to the older definitions of TTL interface or also CMOS. This Pins, usually immediate the controller pins, must not connect to the 3.3 V-level pins of the SPE-Adapter card. For this approach a potential adaption is existing. Hence, only the upper row should be used, or the bottom (lower) row, depending on the kind of the processor pin level.

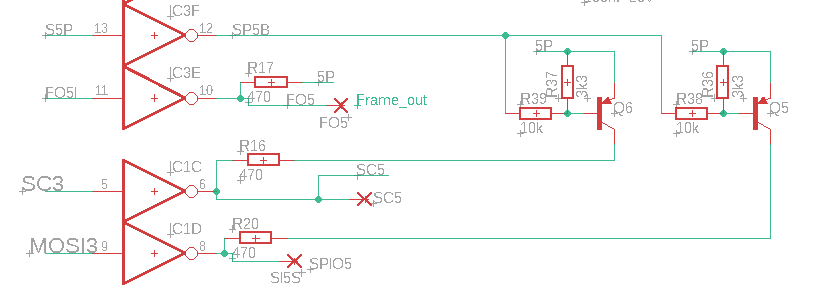

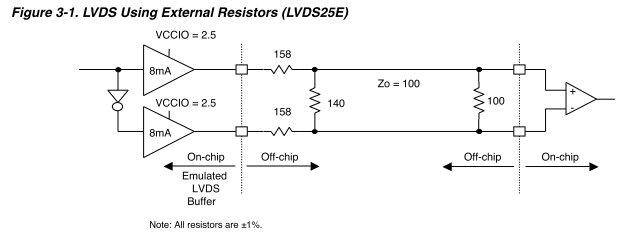

The image above shows a part of the FPGA wiring, especially 5 V inputs.

-

The 3.3 V inputs are immediately connected to the FPGA. It means there are no additional delays and edge reduction for the signals. The pins can be input or output depending on software configuration without additional effort.

You should carefully handled with this inputs, faulty voltage can destroy the FPGA and hence the whole card. But that are known conditions for development.

It is for

-

FO3(A8): frame out -

SC3(A30): SPI Clock in or out -

SO3I(A28) Master Out Slave In for SPI

-

-

Some input pins have voltage divider for 5 V. The same pins are used as 3.3 V input, the 5 V input pin should be left open than. The load current for 5 V and also for 3.3 V input is < 2 mA, 2.8 kOhm on 5V and 1.8 kOhm on 3.3 V. This load current should be admissible. If the resistors will be greater to get a lower load current, then it is possible that the rising and falling time for the edges are too long. One should calculate with ~ 10 pF on 640 Ohm (R’s are parallel for this consideration), it forces ~ 7 ns. You should left open the 3.3 V pin if you don’t need it. Otherwise, you can get a higher parasitic capacity.

This is for

-

FI5andFI3(A25) frame_in signal, Input of SPE card. -

SI5andSI3(A26) SPI-Input, it is MOSI input for SPE-Card as only SPI-Slave or MISO for SPE Card as SPI Master.

-

-

Some input pins have a voltage divider for 5 V, but they are connected too to open-drain output driver for the 5 V level, see next image. The pins on FPGA are independent inputs. The voltage divider uses approximately 1 mA for 5 V output with 1.5 kOhm + 2.7 kOhm as voltage divider. The lower current is necessary because it is a load on the 470 Ohm-driven output, which is hence reduced from 5 V to ~4.5 V. The higher resistors increase the edge times to ~ 10 ns instead 7 ns for a parasitic capacitance of 10 pF.

-

SC5(A17) -

SI5S(B20), this is the SPI-Input for the SPE card as Slave. It is then MOSI possible to connected with SO5 for the other direction, SPE card as master, See chapter SPE card in passive and active mode, with same MOSI and MISO.

-

The 5 V outputs are driven with open drain and pullup:

The "cheap" solution with simple voltage divider and open-drain driver is used, because it is though sufficient and the application for 5 V is not the important one. The open drain outputs are available without additinal effort because some gather for the current source switching are otherwise unused. The effort for an otherwise necessary extra driver circuit is saved.

The 470 Ohm pullup causes a rising edge time of ~ 25 ns on 50 pF parasitic capacity load. This capacity can be occur on longer connection lines to your hardware. But usual it should be lesser, so that 20 ns are not reached. The signals has pulse widths of 50 ns for the SPI clock. So the rising time for the 5 V signals is near the limit but admissible.

The 470 Ohm pullup forces a 10 mA current from the power supply for low level. Hence it is more sufficient to have a inactive high level (as it is usual for the classic TTL signal approaches, "low active". If the 5 V outputs are not used as in many applications, this current can be prevented by two mechanism:

-

With the signal S5P = low (FPGA B3) the source for the current is disabled. This signal

S5Pshould be high for active 5 V levels onSC5andSPIO5. -

If the FO5 Output is not used, it should be held on high level, then the not used output

SO5is high without driven current.

If the outputs are used also as inputs and hence as outputs for the controller,

especially for SC5 and SI5S connected to SO5, then the output of the controller

may need drive 10 mA to low. But the resistor of 470 Ohm is possible to switch off

for this mode. The pin S5P on FPGA (B3) should be set to low for this mode.

The following 5-V signals are driven with this logic:

-

FO5Frame out, driven fromFO5Ion FPGA (B4) without other connections. -

SC5SPI clock output driven fromSC3on FPGA (A30), theSC3is used also as clock input or output for 3.3 V level. -

SO5SPI output driven fromSO3Ion FPGA (A28).SO3Iis also used as SPI input or output for 3.3 V .

For combination of this signal see also chapter SPE card in passive and active mode, with same MOSI and MISO

3.3. Frame signals

-

FI3FI5Frame_in: Low is the inactive level (also if not connected), High (that is >4.0 V on FI5 or >2.7 V on FI3) is the active level.On passive

Frame_inyou can configure the card via SPI with Controller as Master with your specific timing and baud rate, see next chapter. With the configuration you can switch the SPE-card in active mode, only thenFrame_inis used.

If the SPE card is in active mode and Frame_in ⇒ 1

then the SPE cards starts immediately a SPI data transfer

with the SPE card as master. Hence the controller should be programmed

as SPI slave with a data rate of 10 MBit/s and proper DMA for a fast data transfer.

The SPE-Adapter as ring master starts after them immediately a transmitted telegram

which content is determined by further SPI accesses to the controller.

The SPE-Adapter as ring-slave starts further accesses if a telegram is received.

-

FO3,FO5Frame_out: This signal comes from the SPE-Adapter to the controller in any case if a telegram is receiving and the SFD (Start Frame Delimiter) after the sync pattern was detected. +. The pinFO3as a high level of 3.0..3.3 V on a load current of < 4 mA. The pinFO5as a high level of 4.0..5.0 V on a load current of < 2 mA. This signal comes with the low-high edge in a shortly moment after receiving a Start Frame Delimiter (SFD) pattern after synchronization bits, it means the data of the telegram begins. This signal can/should be used to capture the counter of a PLL (Phase Look Loop) control for an interrupt counter. See frame_in and frame_out signals, PWM and time synchronization.

3.4. Connection of the SPE card with the controller for SPI pins

3.4.1. SPE card only used in passive mode

This is more simple for wiring especially for 5 V signals, because the pin direction is defined.

A SPE card only in passive mode cannot exchange data on the fly. See chapter Telegram data words in passive mode (SPE-card is SPI slave). The data on the fly approach needs a fast SPI communication with DMA access. This feature may not available in a cheap controller. Such controllers can be used too with the SPE card, but for less and slower data only. Then this operation is proper.

The controller writes in an independent slower time some status bits to the FPGA as active SPI master. This status bits are transmitted if a telegram is received and forwarded. The next telegram will write the same status bits if they are not meanwhile changed. In the same manner received data are stored only in the FPGA. On SPI master access from the controller this received data are output to the MISO line to store in the controller.

Pin |

Pin SpeA |

FPGA |

meaning (SPE card related) |

SPICLK : out |

SC3: in (FPGA only) |

A30 |

Clock, input |

SPIMOSI: out |

SI3: in (hi 2 mA) |

A26 |

MOSI: input for data from controller |

SPIMISO: in |

SO3I: out (FPGA only) |

A28 |

MISO: output for data to controller |

S5P out :=0 |

B3 |

Switch off5 V output |

|

SC5 in :=0 n.c. |

A17 |

non connected 5 V SPICLK hold on lo |

Pin |

Pin SpeA |

FPGA |

meaning (SPE card related) |

SPICLK : out |

SC5: in (hi: 2 mA |

A17 |

Clock from Controller to SPEa |

SPIMOSI: out |

SI5: in (hi: 2 mA) |

A26 |

MOSI: data from controller |

SPIMISO: in |

SO5: out (hi max. 1 mA) |

A28 neg |

MISO: data from SPEA to controller |

S5P out:=1 |

B3 |

Switch on 5 V output |

|

SC3 out:=0 |

A30 |

Switch off SPI CLK 5 V output |

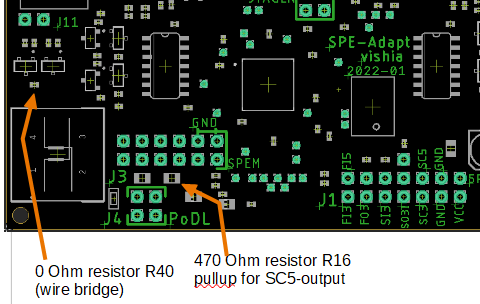

For this mode the clock input is driven with an pullup resistor of 470 Ohm. This is unnecessary but not disturbing if the SPICLK output of the controller can drive 10 mA to low. If it is not so, it is necessary to remove one resistor on the card:

The 0 Ohm resistor can be removed, and perhaps later replaced by a solder drop if the low current of 10 mA is to high.

3.4.2. SPE card in passive and active mode, with same MOSI and MISO

The default mode is the passive one. The card can be programmed via controller

and then switch to active mode. In active mode the outputs are active

only after a leading edge of the frame_in signal.

It means the controller has time to change its in/out pin configuration

if the creation of frame_in from the controller is proper.

In active mode the SPE card uses the SPI interface as Master with "data on the fly" approach. It means an incomming telegram writes data to the controllers RAM immediately after data receiving and gets data for the forwarded telegram in ring topology.

Often controller have only one definition of "MOSI" and "MISO" on the same pins in master and slave mode. It means the MOSI pin is the data output of the controller in SPI-Master mode, but it is also the data input of the controller in SPI-Slave mode on the controller. It means this pin changes its direction depending on the SPI Master/Slave mode.

+

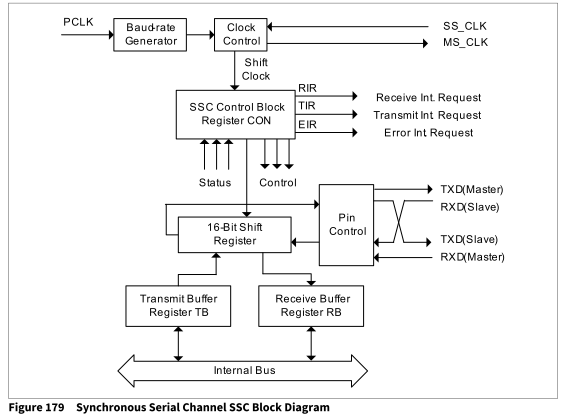

Look right side in a schema for the Infineon TLE987x family..

The image is from the users manual https://www.infineon.com/dgdl/Infineon-TLE987x-UserManual-v01_60-EN.pdf,

Rev. 1.5.0.1. 2020-02-19, page 663. This schema suggests that the same pin is used

for TXD(Master) and RXD(SLave). On page 674 you can see that you have only one choice

for the MTSR_1, it is P0.2, and 4 choices for MRST, for SSC1, but not the same pin

both for input and another both for output for master and slave. Adequate it is for the SSC module.

In this documentation MTSR for "Master Tramsmit Slave Receive" is used

which is the same as the familiar MOSI "Master Out Slave In", same strategy.

Pin |

Pin SpeA passive |

Pin SpeA active |

FPGA |

meaning (SPE card related) |

SPICLK : out/in |

SC3: in (FPGA only) |

SC3: out (FPGA only) |

A30 |

Clock, output and input |

SPIMOSI: out/in |

SI3: in (hi 2 mA) |

SI3: out (hi 2 mA) |

A26 |

MOSI, Master out, Slave in |

SPIMISO: in/out |

SO3I: out (FPGA only) |

SO3I: in (FPGA only) |

A28 |

MISO: Master in, Slave out |

S5P out :=0 |

S5P out :=0 |

B3 |

Switch off5 V output |

|

SC5 in :=0 n.c. |

SC5 in :=0 n.c. |

A17 |

non connected 5 V SPICLK hold on lo |

This above is the same wiring as only passive mode.

Pin |

Pin SpeA passive |

Pin SpeA active |

FPGA |

meaning (SPE card related) |

SPICLK : out/in |

SC5: in (hi: 1 mA) |

SC5: out |

A17 |

Clock |

SPIMOSI: out/in |

SI5S: in (hi: 2 mA) |

SI5S: in unused |

B20 |

MOSI Master out, Slave in |

SPIMISO: out/in |

(not available) |

SI5: in (hi 1 mA) |

A26 |

MISO Master in, Slave out |

S5P out:=0 |

S5P out:=1 |

B3 |

Switch on 5 V output |

|

SC3 out:=0 |

SC3 out:=SPICLK neg |

A30 |

Switch off SPI CLK 5 V output |

For 5 V operation in passive mode of SPE card (SPI slave) it is not possible to read data from the SPE card because the SI5 pin cannot used as Out pin. It means the controller can only program the SPEa card. not get the status. Data reading from the controller is only possible (and necessary) in active mode.

In passive mode of the SPE card the MOSI signal comes from the controller

and is read via the SI5S connection.

But for the active mode this wire "MOSI" should also connect to SO5.

SO5 is driven from from SO3I (FPGA A28).

For the SPI slave mode of the SPE card SO3I is held to low for inactivity.

Additonal the signal S5P is also set to low.

With them both pull up resistors 470 Ohm for SO5 and SC5 are inactive,

so no current is forced. Hence the conditon for the SO5-SI5S connection

is only a load current of 1 mA on high level.

In active mode the SPIMOSI signal is driven from the SO5 output,

which is the negated SO3I as FPGA output on pin A28.

The S5P signal (FPGA B3) is set to 1 for active driving.

This is also valid for the SPICLK output on SC5.

In active mode the SPIMISO is connected to SI5, that is always an input with 2 mA load on high level.

It should be driven from the controller as Slave output.

3.4.3. SPE card in passive and active mode, with same Input and Output

If there is a controller which has not the same MOSI and MISO strategy (same pin function with different direction for Master and Slave mode) but instead the same Input or Output strategy (for master and slave the choice of pin direction is the same), it is a little bit more easier with the connection. But unfortunately usual the most controller does the same, Using the same pin functionality for MOSI and MISO and instead switch the direction.

Pin |

Pin SpeA passive |

Pin SpeA active |

FPGA |

meaning (SPE card related) |

SPICLK : out |

SC3: in (FPGA only) |

SC3: out (FPGA only) |

A30 |

Clock, input |

SPI-out: out |

SI3: in (hi 2 mA) |

SI3: in (hi 2 mA) |

A26 |

MOSI: input for data from controller |

SPI-in: in |

SO3I: out (FPGA only) |

SO3I: out (FPGA only) |

A28 |

MISO: output for data to controller |

S5P out :=0 |

S5P out :=0 |

B3 |

Switch off5 V output |

|

SC5 in :=0 n.c. |

SC5 in :=0 n.c. |

A17 |

non connected 5 V SPICLK hold on lo |

This above is the same wiring as only passive mode.

Pin |

Pin SpeA passive |

Pin SpeA active |

FPGA |

meaning (SPE card related) |

SPICLK : in |

SC5: in (hi: 2 mA |

SC5: out |

A17 |

Clock |

SPI-out: out |

SI5: in (hi: 2 mA) |

SI5: in (hi: 2 mA) |

A28 ne |

MOSI for SPE slave, MISO for SPE master: |

SPI-in: in |

SO5: out |

SO5: out |

A28 |

MISO for SPE slave, MOSI for SPE master: |

S5P: out:=1 |

S5P out:=1 |

B3 |

Switch on 5 V output |

|

SC3: out:=0 |

SC3 out:=SPICLK neg |

A30 |

Switch off SPI CLK 5 V output |

4. SPI data interface

4.1. Active and passive mode of the SPE card for SPI

The SPI (Serial Peripheral Interface) is used in two situations:

-

1) Passive mode: Configuration of the card and slow access.

-

2) Active mode: Especially for data handling during communication (telegram operation data on the fly)

4.1.1. High active frame_in signal for SpeA-SpiMaster access / frame_in low for controller master access

Generally, if the signal frame_in comes to the SPE-card with high-active level (Pin J1.1 or J1.2, FI3 or FI5),

then the SpeA-card starts an active SPI access as master. The controller should be prepared firstly.

If the SpeA-card should be configured with Controller-SPI master access, frame_in should held on inactive low level.

The pins of the SPI communication are either driven as output or they are inputs. All pins are switched between SPI master or slave role:

-

SPICLK: Output from master. -

SPIMOSI: Master out for data from master, Slave in -

SPIMISO: or …SOMI Master input for data from Slave

The role of the pins is not changed, the SPIMOSI is always the master data output from the current master.

It means it is the output from the SpeA-Card if the card accesses via SPI if frame_in is active,

then the controller should be switched before in SPI slave mode, and hence its SPIMOSI is an input pin.

If the frame_in signal is inactive low, the controller can but need not access the SPI as master.

The SpeA-card switches all SPI pins to a tristate with pulldown, and uses it as input to listen for the SPICLK,

so the pins remain low as output as last master active state if the controller does not drive the pins.

The controller can now produce a SPICLK signal as master, then the SpeA-card answers with an activated SPIMISO pin

immediately after clock detection with the data.

After a small time (one clock period) after the last SPICLK the SpeA-card switches this pin again as tristate (input) with pulldown .

So the controller can switch to SPIslave after its access

and before frame_in is activated, which drives the SPIMISO as output from the controller.

If the controller will then drive the frame_in active high, then before that or a small time after activating frame_in,

the controller should set its SPI access in the slave mode. Hence the controller does not drive SPICLK and SPIMOSI,

but it drives SPIMISO as data pin.

Additionally, the SpeA-card contains a "collosion detection". If the SpeA-card drives SPICLK, then it reads back this pin in the next 10 ns clock. If there is a difference between the output and the read back input, the SpeA-card switches off both the SPI-master access as also the transmission of a telegram. The may be then faulty (missing data, CRC fault). This can occur especially in development and test situations if the controller software is not yet perfect. To detect this situation, the led near the SPI connector flashes rapidly for one second after the collision.

4.1.2. SPE card in passive mode as SPI slave for configuration and slow data access

For the first configuration after reset, the SPE-adapter is in passive mode, as slave for SPI communication. It means the controller can access by its own timing with its own any bit rate. You can write some configuration words.

Using a slower SPI Bit rate can be necessary also in running mode if the controller cannot handle really a fast access with DMA. Then this mode should be used also in running mode.

In this mode the SPE-card is the SPI slave, and the controller can act as SPI master.

After configuration you can:

-

remain in passive mode, either for slow data access or for further configuration maybe for tests. If the card is only used in passive mode, you can use the wiring due to chapter SPE card only used in passive mode.

-

switch to active mode, see next chapter Switch to active mode.

-

anytime reset to passive mode indepenedent of the state, see chapter Reset the SPE card to psssive mode for frist cmd

4.1.3. Switch to active mode

If the SPE card is in passive mode, a written cmd with bit 15 = 1 switches to active mode.

Then firstly, all other cmd bits are ignored. It means no more data words are expected in passive mode.

See chapter Command word bit meaning.

Then the SPE card generates its first active access only after a leading edge of frame_in.

The first read data word is again a cmd word which’s content determines the following sitation.

In programming after configuration, it is possible firstly to reporgramm the SPI adapter

for slave mode on the controller.

If outputs especially for the clock are working against, then with the same level (passive low),

so no high current can occur. The active SPI access from the SPE card is so long non active

as the frame_in signal has not a leading edge.

If the programming of SPI as slave on the controller is done,

then the counter (usual PWM signal) should be programmed to create the frame_in signal.

See chapter frame_in and frame_out signals, PWM and time synchronization

If this counter is started, the SPI access from the SPE card occurs,

with the correct prepared slave-SPI on the controller.

4.1.4. SPE card in active mode as SPI master

In this mode the time of data transmission depends of the SPE-card respectively the telegram communication.

The SPI on the SPE-card is the master, the controller should be programmed as SPI-slave.

For that the frame_in signal is essential, see chapter frame_in and frame_out signals, PWM and time synchronization

In active mode the SPE card forces an SPI access to the controller

immediately after the leading edge of frame_in for at least the cmd word.

Depending on the content of the command word either some more configuration words

are requested from the SPE card, and status informations are written,

or telegram content is requested and written.

For telegram communication the first data word to transmit is read immediately, so 32 clock edges are transmitted. The following requests depends on the state of the SPE card as the SPE master for Ring topology or for Bus/Multidrop topology, or as slave for Ring topology.

The principle here is "just in time". It means data should be read and written from and to the controller RAM in that moment as they are necessary to transmit and received. This allows the opportunity that the software on the controller prepares the data a short time before transmission, and evaluates it already a short time after receiving in a synchronized process over all participants. Only with that approach a fast communication cycle is possible. The bit rate on SPI is 10 MBit/s, it should be the same as for SPE-Communication.

4.1.5. Reset the SPE card to psssive mode for frist cmd

In passive mode of the SPE-card as SPI slave a low-high-low sequence on frame_in

forces a reset of the internal SPI data counter so that the next SPI write access is again a cmd word.

It means, during configuration the frame_in should not be used and hold on inactive level.

A active-inactive sequence can be output immediately on the 'frame_in' output pin to reset the SPI data sequence.

In active mode of the SPE-card as SPI master generally a leading edge on frame_in

forces reading the cmd word, independent of the necessity of further data words

or maybe expected but not received telegram data.

If this cmd word has bit 15 = 0, then the passive mode is switched on.

To execute a safe operation independent on the situation you can

-

firstly stop the

frame_inoutput by the normal PWM operation, -

then reporgramm the

frame_inand also the 'SMISOMI' pin as normal binary output for low level. -

Then manual output the

frame_insignal which is a leading edge. -

Then wait for twice SPI word time.

Note that only the inactive level of the frame_in signal does not already abort

the active SPI communication, if further data words are expected

or requested due to the length bits of the last cmd.

It means during the leading edge of frame_in a data word can be currently still received.

Only the the next word is the forced cmd word. But because of SPISOMI = 0,

all bits are detected as 0, and the cmd = 0x0000 is read at least with the second access

after the currently running. Then it is switched to passive mode.

4.2. Meaning of the data via SPI

4.2.1. Command word bit meaning

The first word (16 bit) either read from the SPE card as SPI master immediately after a rising clock of frame_in

or as first word from the controller as SPI master after reset or as next after the writing sequence is the command word.

The bits in this command word have the following meanings:

| bit | val | mnemonic | meaning |

|---|---|---|---|

15 |

0 |

Passive mode: The SPE card is switched to or remains the SPI slave. It means it expects the given number of following words due to bits 14..12 and 7..0 as SPI slave from the controller as SPI master, and expects afterwards the next SPI word again as cmd word from the controller as SPI master. |

|

~ |

1 |

Active mode |

The SPE card is switched to or remains the SPI master. It means the SPE card will be create following SPI accesses by itself. This is either furthermore continued if the SPE card was in active mode also before or it is handled see chapter Switch to active mode. |

14 |

0 |

Data mode: The next read and write words are associated to a telegram content. Bit 9..0 determines how many words are processed with a telegram. See chapter Telegram data, generally |

|

" |

1 |

config |

Config mode: The next read and write words are configuration words. Bit 9..0 of this command word describes how many config words are following. See chapter Configuration data |

13 |

0 |

TelgRx, SPE-Slave: The SPE card is the communication slave in the ring. See chapter Telegram data words in active mode, expecting a received telegram |

|

" |

1 |

SPEmaster |

TelgTx, SPE-Master: The SPE card is the communication master in the ring. See chapter Telegram data words in active mode, SPE master. |

12 |

0 |

xx |

|

" |

1 |

xx |

|

11 |

0 |

Gap: On end of the telegram the output goes to tristate to prevent driving the line. This is necessary for multidrop bus communication. This phase is the "gap" between telegrams. |

|

" |

1 |

noGap |

No Gap, Ring: After end of the telegram the sync pattern is transmitted

instead going to tristate on the line. This is proper for ring communication.

The line remains active. This is proper for a reduced gap respectively fast synchronization.

The number of sync bits can be till at least 24, that is 2.4 µs.

The number of sync bits are determined from the telegram length (data byte 0)

and the real time of the |

10 |

0 |

Transmission as master with SPE X1 connection, the SPE X2 connection is the receive port. |

|

" |

1 |

Transmission as master with SPE X2 connection. For ring topology the ring is used in the reverse direction. This is necessary to detect a failure (break) in the ring. For multidrop bus topology the X2 plug is used for the following telegram. |

|

9..0 |

n |

mWord |

Number of following words read and write via SPI. This word are either for following configuration infos or as number of 16 bit words in a telegram, depending of the bits 14..12. With this definition the maximal length of a telegram can be 1024 word or 2048 byte. It means the standard for normal telegram communication with 1522 byte is possible. But the number of bytes is even. |

4.2.2. Configuration data

The next words from controller to SPE card are configuration words. The next words from the SPE card to the controller are state informations.

The config and state words are either transferred by the SPE card in active mode

as further words after this cmd after the leading edge of frame_in (bit 15 = 1),

or they are expected from the controller if the SPE card is and remains in passive mode (bit 15 = 0).

If you want abort the configuration data stream in SPE card passive mode you can create

a leading and falling edge of frame_in to reset the SPE card. See <<>>

In configuration mode the following word after the command have a special meaning in bits:

| bit | val | mnemonic | meaning |

|---|---|---|---|

15 |

0 |

The following words describe the bytes which should be exchange for telegram forwarding. |

|

" |

1 |

The following words describe the bytes which should be write to the internal register for active SPI access from the controller (passive mode). |

|

14..4 |

x |

todo |

|

3 |

0 |

Not using the 5 V driver. The outputs for 5V signals are set all to 0. Hence the connected open-drain-driver are switched off. The output level is high. (No additional driver current) |

|

" |

1 |

level5 |

Using the 5 V driver. Independent whether this output values are used, this forces a higher power consumption because the output driver have 470 Ohm pull up. This forces 10 mA per signal in low mode. |

2 |

0 |

Polarity 5 V SPICLK active low: The SPICLK signal is driven active low with falling edge for data output. This has the advantage of lower power supply because the inactive level is high with no driver current. This is only relevant in telegram mode, SPE-card is SPI master. |

|

2 |

1 |

Polarity 5 V SPICLK active high: This has the disadvantage of more power consumption (10 mA) because in the inactive low output the driver are switch down with open drain via a 470 Ohm resistor. It is ~ 10 mA |

|

1 |

0 |

Polarity 5 V for data negated: Data output bit =0 forces pin=high. But in inactive mode, the data output is high to prevent unnecessary power consumption. |

|

" |

1 |

Polarity 5 V for data non negated. |

=

All other configuration words defines in bits, which data bytes should be transmit forward for a SPE-slave, and which bytes are exchange with content of RAM.

For a SPE-Master this config words are not necessary. Note that for multidrop bus technology the SPE-card is always the SPE master.

Any bit of a configuration word is related to one byte for data transfer.

-

The bit 0 is related to the first byte for transmission. That is the high byte of the first data word for 16 bit memory access via SPI.

-

The bit 1 is related to the second byte for transmission. That is the low byte of the first data word.

-

Etc. You need upto 95 configuration words for 1520 data bytes for a telegram. But may be not this full length is supported by the FPGA, if the FPGA should contain more logic and it is used only for a fast cycle time. For 50 µs cycle you need only 3 configuration words for the maximal 48 Byte telegram length.

Depending on bit 15 of the first config word, the bits are regarded

-

either to the data words which should be exchange forward in the ring

-

or to the data words which should be stored internally in FPGA register for a active controller access (SPE card is passive), see chapter Telegram data words in passive mode (SPE-card is SPI slave).

4.2.3. Telegram data, generally

In passive mode (bit 15 = 0) special telegram register are set and read which determine the content of the next telegram whenever it will be received and forward transmitted, see chapter Telegram data words in passive mode (SPE-card is SPI slave).

In active mode (bit 15 = 1) the first data word to transmit is read from the controller immediately after the cmd word.

For the next words the "data on the fly" approach is used:

The next data words are read and write either if a telegram as SPE slave is received (see chapter Telegram data words in active mode, expecting a received telegram or as SPE master the words are read with afterwards to transmit, see Telegram data words in active mode, SPE master. The written data to the controller (MOSI) are the received content from the other SPE connection.

4.2.4. Telegram data words in passive mode (SPE-card is SPI slave)

This mode is proper if the SPE-card is used with a cheap controller which does not support a fast SPI communication as slave with DMA. For such controller the 'data on the fly' approach cannot be used. The command bit 15 = 0 should be set anyway.

For this passive mode of the SPE card,

-

some (not all) received data words are stored inside the FPGA to read out via SPI.

-

some data words to transmit forward are stored inside the FPGA from SPI writing before.

Which data words, this is determined by the configuration.

Hence, the received information is store firstly only in the FPGA and the information to transmit is stored and used primary internally. The SPI access does not act as the 'data on the fly' approach, if can be used to write and read the data in a slower time.

Because data consistency should be preserved, the data get valid only after the last write access, and read data are hold from the first read access to the last

Therefore the data are double buffered. If the last data word was written and read, the written data are designated to use for transmission in the next telegram and the read data are designated to free for fill. There are filled with the content of the next telegram.

Hence, the data are consistently as content of one telegram. If the data are not renewed, the next transmitted telegram uses the same data, and the received data are ignored.

This approach enables a slow communication inside a fast Ring topology communication between other stations.

The controller should read and write this data words via SPI as master,

-

A SPI access starts always writing the command word and reading the first state.

-

The second word contains always in bit 15..10 the own sender address, which is replaced by the forwarded telegram.

-

The following read and written data via SPI are related to that positions in the telegram, which are designated to replace for the forwarded data and designated to store as read data. All other telegram content is not related. It is forwarded 'as is' and not stored.

Any data byte which should be exchange is presented by a half word in the descending order from this written data register. For received data only that bytes are written in the data register which are marked with a bit in the further configuration words after configuration word 1 with bit 15 = 1.

This reduces also the effort of SPI communication in the controller. If for example the telegram consists of 1000 Bytes, and only 20 Bytes or 10 data words are related to this controller, also only this 10 data words should be read and written.

4.2.5. Telegram data words in active mode, SPE master

This should be used either for the SPE master in Ring topology or to transmit data on a Bus/Multidrop technology.

If the cmd word is set to 0b111x’xxxx’xxxx’xxxx then it is active mode (cmd bit 15) as SPE master in Ring or Bus/Multidrop topology (cmd bit 13) and telegram data (cmd bit 14).

Then immediately after the cmd word the first data word is requested. Next data words are requested one after another as continues bit stream from SPI, but firstly with a little gap in the SPICLK stream. This is due to inner time organization. For the SPI programming it is not essential.

This data words are transmitted to the requested SPE output (due to cmd bit 10).

The other SPE connection can receive data. In the Ring topology this is the back connection. Due to the delay times the first words are emtpy (content 0), because data are not received. Then the received data comes synchronous to the transmitted data, but delayed.

In a non-Ring topology the other SPE connection cannot be used, expecting to see what is happen on the bus, for collosion detection. Then the same data should be received as transmitted, with a delay of 1 data word because of the internal shift operations.

4.2.6. Telegram data words in active mode, expecting a received telegram

Firstly as described above the command word and one data word are read from the SPE card

after a leading edge of frame_in.

Then received data are expected. If they comes, the SPI accesses are forced

from the SPE card to write the data to the controller. The read data can be used

to transmit it to the other SPE connection, either for Ring topology

or for bus or star topology as second output maybe for debugging.

So long as data are expected and not received, no further leading edge of frame_in

should be created.

A leading edge of frame_in should be created either to reinitialize the receiving,

or to transmit data.

If a receiving telegram comes, with the SFD bit (Start Frame Delimiter) the signal

frame_out is set, and if the data words ends, frame_out is set to false.

Especially the last one can be used to invoke an interrupt to process the receiving data.

4.2.7. Telegram data words in active mode, SPE slave in Ring topology

From side of the SPE card it is primary the same behavior as described in the chapter above.

The difference between Ring topology and the other ones (Bus, MultiDrop, Star) is: The received telegrams are expected in a constant cycle, the content is forwarded transmitted to the other SPE output, some data are replaced.

It means, for not Ring topology, the receiving is intialized with SPI + DMA initialization,

and a given frame_in edge. Then it is waiting a longer time till a telegram comes.

A further frame_in without receiving should only outputted for a longer time out,

in range of millisec.

But for the Ring topology the cycle is determined.

It may be down to 50 µs, or in small ms range.

In the Ring topology only one station have to be the SPE master. All other stations should be slave. A slave forwards a received telegram independent of programming with unchanged content. Only the bit1 15..10 of the first data word are automatically replaced with the own sender identification.

To receive data and exchange data on dedicated positions

the SPE card should be triggered with a frame_in leading edge

before the receiving is expected.

It means a synchronization of the interrupt cycle for telegram communication

should be already established. See chapter frame_in and frame_out signals, PWM and time synchronization.

If this is proper, the cyclic interrupt for SPE communication should be invoked

a sufficient time before the received telegram is expected.

This should be done before the leading edge of frame_in, usual with zero crossing

of the PWM timer. The cyclic SPE interrupt should firstly initialize the SPI communication

for the expected telegram, set the DMA to the start address etc.

Before this, of course, the last received data can be processed.

Another possibility is: use of two buffers (alternating buffer principle) for data reception.

After initialization of the SPI and DMA in a dedicated time, the frame_in should be come

from the PWM module, before the telegram receiving starts.

Immediately after the leading frame_in edge, before telegram data comes,

two words are read and written via SPI (SPE card is master, active mode).

-

The first read word is the command, as in any case.

-

The first written word is the state of the SPE card.

-

The second read word is the first data word to forward in transmission. It contains in bit 15..10 the own sender address for the Ring data frame. The length bits 9..0 should be 0, then the information about the received length is forwarded and used. But the telegram can be modified in length too with a given new length in bits 9..0 of the second word.

-

The second written data word is the second state word of the SPE card which contains the stored own sender address in bits 15..10.

Then the SPI communication pauses till data are received.

-

If the first data word of the receiving telegram comes, it is written via SPI/DMA to the controller. Similar with the SPI communication the next data word for forward transmission is read.

-

The immediately forwarded data word was already read as second SPI word, and it is now used.

-

Similar with the SPI the next data word is read for forwarding. It is necessary immediately after, for the current telegram communication. This data word can be prepared in the RAM immediately before, synchronous, so the newest value is transmitted.

-

Etc. for all received and to transmit data words. Note that not all forward transmitted data words are exchange from the controllers RAM content, only that words which are set to exchange by configuration. The grant of the data in the received telegram may be forwarded unchanged, because it is the content from another station to receive in another station. Only that words are replaced which should be come from this station. But all words are read from the SPI communication, unnecessary. This is because the SPI communication cannot be decide whether reading is necessary. firstly the already read first data word is transmitted forward.

-

The last received data word is the CRC.

If a telegram is not received, because broken wiring or such,

the next SPE interrupt will be newly initialize the SPI and DMA,

and the next leading edge frame_in starts newly the receiving process.

4.3. Default SPE master selection

By default behavior, the SPE card act as slave for the Ring topology. This is necessary, because the controller software may be wrong, and the ring should be work nevertheless. A reset on the controller should be execute a proper state for all other stations in the ring.

But if you have only SPE-slaves in the ring, a faulty received telegram circles in the ring. A master is necessary to break this behavior.

Thats why the master can be selected hard wired. The standard FPGA uses the pin A16 for selecting master = lo or slave = hi (with internal pull up). It means you need a pin header and a jumper to select the master property.

5. frame_in and frame_out signals, PWM and time synchronization

5.1. frame_in meaning

The frame_in is the first important control signal from the controller to the SpeA-card.

-

If

frame_inis passive, low, the SpeA-card does not transmit a telegram as master. It ends a running transmission without CRC calculation immediately. But it can receive and forward a telegram in ring topology as slave. That is the default mode also after reset if the master-jumper on J3.9-10 is not set. It means if the controller does not work or it is not connected, a SpeA card acts as Spe-Ring Slave if it is not jumpered as master. -

If

frame_inis passive, low, the SpeA-card does never access the controller as SpiMaster. Instead, the controller can access the SpeA-card as SPI-master, the SpeA-card listens on the SPICLK pin. -

If

frame_ingets active high, leading edge, then the SpeA-card start transmission a telegram as master if this is enabled with Bit13 in cfgWord 0x01. -

If

frame_ingets active high, leading edge, the SpeA-card starts access the controller as SPI-master if this is enabled before by configuration . It means the controller should be prepared for SPI slave access.

In active mode it forces the SPI access.

In passive mode it resets the SPI access to receive the next written word as cmd, see chapter Reset the SPE card to psssive mode for frist cmd

5.2. frame_out meaning

The frame_out signal from the SPE card (output) to the controller

is set to active (high) with a receiving telegram after correct received synchronization

if the SFD (Start Frame Delimiter) is detected.

Because the internal clock in the FPGA is synchronized,

this signal have a jitter of typical 10..30 ns only.

-

It can be used to capture the current counter of the running PLL for time synchronization.

This frame_out signal is reset to inactive (low) after receiving the whole telegram.

This is either if the clock synchronization is lossed because of a gap between the telegrams,

especially for Bus/Multidrop topology,

or if the amount of data words are expired for Ring topology.

This amount of data words comes either from the first data word, bit 9..0,

or also from configuration.

Especially for the gap detection in Bus/Multidrop topology this "end of telegram" information can be used to trigger an interrupt to evaluate the telegram.

For Ring Topology with cyclically communication this is not usefull, instead the PWM should be synchronized, see chapter PLL and its synchronization.

5.3. PLL and its synchronization

In the master the communication is sent very time deterministically with the falling edge of the

frame_in signal.

Thereby the internal clock in the FPGA is synchronized to +- 15 ns (jitter 30 ns

measured) to the falling clock edge of the frame_Inp.

In the slave the SFD bit (Start Frame Delimiter, last bit of the synchronization pattern) generates

the signal frame_out with Lo-Hi transition. This signal gets back to inactive (low)

if the telegram is finished.

The simple scheme of time synchronization is:

-

Master bumps the communication to Frame_Inp Hi→Lo.

-

If the telegram is completely received in the slave stations (Frame_Out Hi→Lo), then an interrupt is triggered there for processing.

Thus the master determines the clock, all slaves react. If, however, a slave emits a PWM signal (pulse width modulation) that has a hardware-defined period, then this should be synchronous with the received data or with the time cycle of the master. The same requirement arises for transducers with a cycle of averaging. If no effort would be made in this direction, then the measuring and setting cycles would adjust floating to each other, because the quartz clocks are never exactly the same on longer times. The result would be fluctuating dead times in the closed loop of the control. For simple and slow controls this is no problem (e.g. temperature control of radiators, light brightness or similar). However, this is a disturbing effect for electrical controls that rely on the short cycle time.

Controllers often have PWM modules that are additionally equipped with a so-called "capture" option (capture of the counter status with an input signal). With this possibility, the PWM can be controlled as an actuator in particular, but also with measuring controllers, so that the cycles are stable to each other with low jitter. With regard to crystal accuracy, only standard requirements are to be met, see the example calculation below.

The PWM as a time-determining element is adjusted in its period duration in each cycle with a so-called PLL control (Phase Look Loop). For example, if the crystal frequency of a controller is increased by 0.1%, then instead of a standard 2000 for 50 µs counted with 25 ns, a 2002 is written in, which can jump between 2001 and 2003 depending on the time situation. Thus the own cycle jitters around the resolution of the PLL by +- 25 ns.

If the cycle of the PLL control is used for the internal software of the controller, the measurement, and the output values (for example PWM for electrical valves) have the same synchronized cycle time, but also the jitter. For an integral mean value of measurement signals this can be considered in most cases. An actuator would fluctuate in the per mill range because of the limited resolution, which is usually not a problem. An PWM output may have a "digital noise" due to this jitter in range of lesser 1 %, which is filtered by the natural time constants.

5.4. Internal clock synchronization in the FPGA

It is important for the SPE communication that the time of the cycle start in the master is

transmitted to all slave devices as accurately and jitter-free as possible.

For this purpose, the FPGA contains a synchronization of the stepped clock of 100 ns

for a bit width of the 10 Mbit/s SPE communication to the frame_in edge in the master

and to all receive bits in the slaves.

Synchronization takes place during reception of the sync pattern (synchronization bit sequence).

The stepped clock is briefly increased or decreased to 9 or 11 crystal clock cycles (10 ns, 100

MHz crystal). This is allowed in the sync pattern. The correction is made up to 5 times distributed

over the entire pattern depending on the position of the bit edges. Thus the internal clock is shifted

by + or - 50 ns each time. In the further course of the telegram a small deviation is then assumed.

This should be less than 2 10 ns cycles for a telegram runtime of 40 µs. This requires a quartz

tolerance for the FPGA SPE connections of 20 ns/40 µs = 0.5 ‰, usually observed by standard

quartz crystals. For a longer runtime of a telegram, for example at 1500 bytes (1.2 ms), already

about 20 ppm crystal accuracy would be required. However, it is also possible to tune the bit width

in the telegram between 90..110 ns, with a slightly increased probability of transmission errors.

6. Definiton of the layer 2 of OSI for a fast cycle

The layer 2 of OSI is the data link layer. For a free Ethernet communication the data link layer should contain source and destination addresses, and the type of data.

6.1. Modified frame for fast ring topology

The meaning of the words of the data link layer accordingly standard IEEE 802.2 are not necessary for a ring topology in a defined manner because the source and destination are defined by the wiring. Also the other data are not necessary if all station understand the changed data frame in the same kind.

Of course it is not possible, also not for tests (for example using Wireshark as test tool) to transmit the data alternatively outside this specific ring.

The change of the meaning of frame data is done firstly to reduce the overhead, because the goal is, communication cycle of down to 50 µs. That allows only 62 Byte in sum inclusively Sync, SFD, CRC, gap.

In the non-gap mode, only possible for ring communication, the gap is summarized with the Sync pattern.

-

The sync phase needs at least 24 bit or 3 bytes. With the SFD it is 4 bytes (31 sync bits and the SFD).

-

The CRC is used accordingly to the standard, 4 Byte.

-

After the SFD two bytes are used for the length and the sender address. If it is seen as 16-bit word the bits 15..10 contains the sender address and the bits 9..0 contains the length. Because of the transmission of high byte first (big endian approach) but in a byte the LSB first, the really bit order is 8..15, 0..7.

-

The remaining 52 byte can be used for data.

If the telegram cycle has a jitter from up to 1 µs due to controlling oscillations to the PLL control for the cycle time, it changes the number of sync data bits till 21 bit. This is the limit.

The next schema shows the telegram frame, the second line shows the number of bits per element.

+-----------------+-----+---------------+-------------------+-----+ | sync bits | SFD | sender length | data | CRC | | min 21, or more | 1 | 6 10 | 0..8*1500 | 32 | +-----------------+-----+---------------+-------------------+-----+

-

The number of data bits depends on the required cycle, it is 52 for a 50 µs cycle or the full range of 1500 Byte for a cycle > 1.2 ms.

-

The length are enough to determine 1023 data words or more as 1500 Byte.

-

The sender address is limited to 63 different ones. It means no more station should be used in the ring. It seems to be enough.

6.2. Standard layer for multidrop bus or Switch/Router connection

For Multidrop Bus or Star topology for a Switch or Router connection

a station should be set for receiving firstly to listen on incomming telegrams.

This is described in chapter Telegram data words in active mode, expecting a received telegram. If the telegram ends,

an interrupt can be generated with the trailing edge of frame_out.

The controller now should evaluate the telegram content. The FPGA on the SPE card does not support that. Because of the full frame for telegram transmission due to OSI level 2 and 3 is received, the destination address should be checked whether this telegram is for the own.

If a transmission is required because it is requested by an incomming telegram, the SPE card should be programmed as SPE master to start the transmission. All data to transmit, also the frame data comes generally from the RAM of the controller via SPI access with DMA. It means the data should be proper prepared.

This occurs in millisec times because the data rate is 10 MBit/s. it is 1.5 ms for a telegram with the full length of 1500 Bytes. A controller should have enough time to prepare such telegram communication.

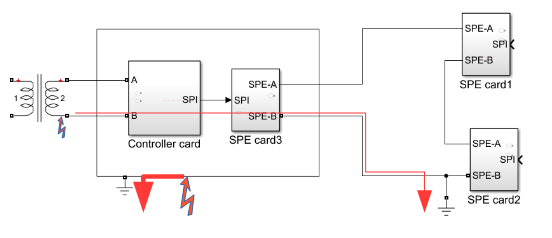

7. SPE ring topology with PC connection

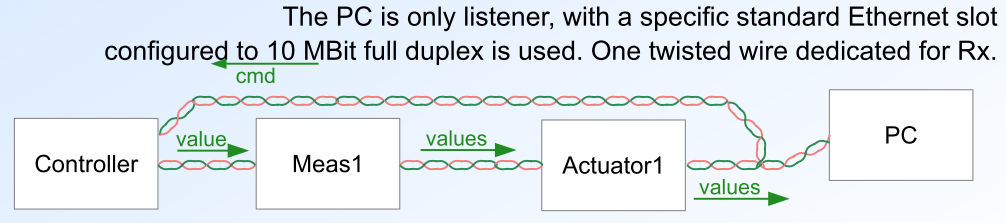

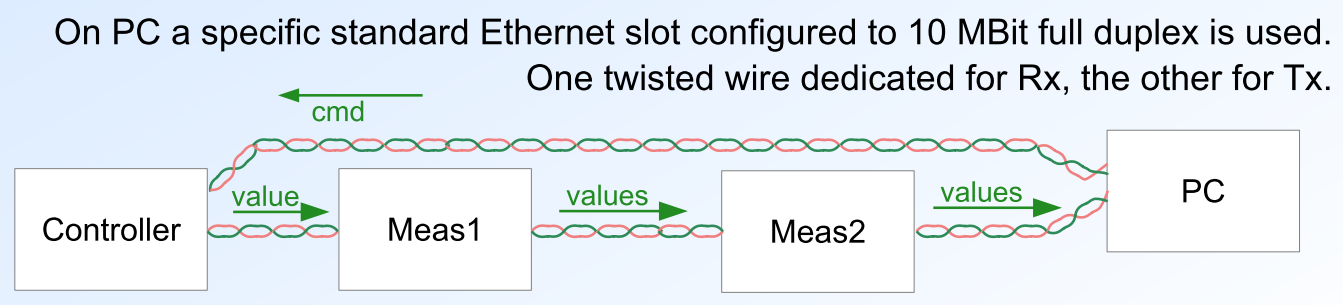

This operation mode can work with cycle times down to 1 ms. Some embedded control stations are connecting together with a ring topology, which allows communication in one cycle with one telegram with all stations in the ring. The PC is only the "also receiver" for all data, which can be used hence for evaluation for example for predictive maintenance, and the PC can transmit control values in telegrams in a slower respectively non synchronized cycle (millisecond range).

The example image shows left the controller, which is the source of the cycle clock, and some other stations following, which can be used for measurements and also as actuator, or which can be other controllers as slave for the cycle clock. The PC comes as last in the ring. The ring is closed to the master controller, which can read out all data from all stations before, but the same data are also transmitted to the PC without additional effort. The telegrams are due to standard, UDP, so that the telegrams can be routed in any PC network.

The PC should transmit control information for this application with a second connection. The SPE ring cannot be used, because the PC cannot act as station in the ring, a PC is too slow. Telegram communication also with Gigabit connections are fast by itself, but the evaluation of telegrams in the PC operation system and adequate processes, and hence also the forwarding of telegrams in the ring can only be done in millisecond ranges.

A more simple solution only for measurement data can integrate the PC directly in the ring, where as the PC breaks the cycle:

In this constellation the Controller does not receive the telegram back from the ring. It means it is only the cycle source and one of the data sources. The controller receives command telegrams from the PC. This is a proper solution for only data acquisition.

For this solution the free SPE rx input of the Controller can be used to receive telegrams from the PC. But of course because a lesser timing of the PC this is not in the exactly 1 ms time step. It is for a few milliseconds, but really fast enough for normal Operation and Monitoring.

7.1. Connectivity to the PC

The PC needs a negotiation about the connection. For standard Ethernet connections this negotiation clarifies the Baud rate, 10 / 100MBit/s or 1 GBit/s, for 10 or 100 Mbit/s the usage of the rx and tx wires, and of course firstly the state of connection itself.

For the 10 Mbit/s it is sufficient that the Source transmits on the tx wire so named NLP pulses: https://en.wikipedia.org/wiki/Autonegotiation. That are positive 100 ns pulses in distance of ~ 16 ms. FLP is not necessary. If only NLP pulses are detected by an Ethernet slot on PC, the baud rate of 10 MBit/s is selected automatically, and the Tx wire is detected. (Older Ethernet Slots needs so named cross-cable, but this is no more true today, it is detected by this NLP pulses which line is used for Rx and which for Tx).

But there is a small problem: If the controller runs as shown in the first image, in an own ring with the PC only as listener, and the PC is connected afterwards, then Tx line transmits already telegrams. Because the telegram sequence is high (1..2 ms), no NLP pulses occurs. Then the PC does not recognize the connection. To connect the PC it is necessary that the ring communication for the controller application stops, then NLPs are transmitted, the connection is established, and then all can work.

A second problem in this constellation is: The PC may transmit sometimes so named ARP telegrams (https://en.wikipedia.org/wiki/Address_Resolution_Protocol) and requests an answer for that. But in this constellation the controller does not receive the ARP telegram, it has not a receive input. Hence this solution can only work if a special solution on PC side, maybe a special SPE switch, exists.

This problems are not given if the PC is completely in the ring, the controller receives also telegrams from the PC. For this solution the following situation is given:

-

The controller may transmit telegrams for the measurement, without a listening PC. In this phase, the last station does not transmit the telegram, it transmits NLP pulses instead. But the controller and the measurements can work already, with the telegram from the controller to control and synchronize the measurements in time.

-

The PC is then connected. With the connection it transmits some ARP telegrams, which are answered by the controller and forwarded from the last meas station to the PC.

-

The PC can now transmit command telegrams, because now it knows the MAC address of the controller (by ARP).

-

With the command telegram now the controller can select the correct IP adress, MAC and the Port for the PC, and now the PC receives all data telegrams.

A solution for the connectivity for the closed ring for the controller application is:

Usage a second SPEa card only for the telegram input, the input can control the telegrams from the controller through all measurement and actuator stations in the same way as the only measurement forward to PC solution.

7.2. Telegram forwarding for only data acquisition constellation

This is in case of the last image in the chapter above. In the normal working mode the controller creates telegrams, which are forwarded from all stations and filled in with data from the measurement stations. The telegram arrives on the PC and can evaluated there. The Controller is always sensitive for command telegrams.

The problematically case is, that the overall association of all stations should answer to the PC with some special telegrams for routing, the so named ARP telegrams. ("Address Resolution Protocol"). An ARP request is received by the controller. The answer should be prepared also by the controller, but forwarded through all stations to the PC. The whole associations of all ring topology stations answers or are seen as only one station with one IP address and one MAC address. Hence, the outer stations should be forwarded the telegram only, without evaluation. The same approach is given for a ping telegram, which should also be possible.

The other stations are prepared normally for receiving a value telegram. It means the data are written in positions in the RAM for measurement data, and also especially data are read and replaced in the telegram with the own measurement data. To prevent doing the same for a ARP or ping telegram the FPGA detects the telegram type and todo detecting content and use switch buffer.

7.3. Timing example for ARP telegrams inside the meas data telegrams

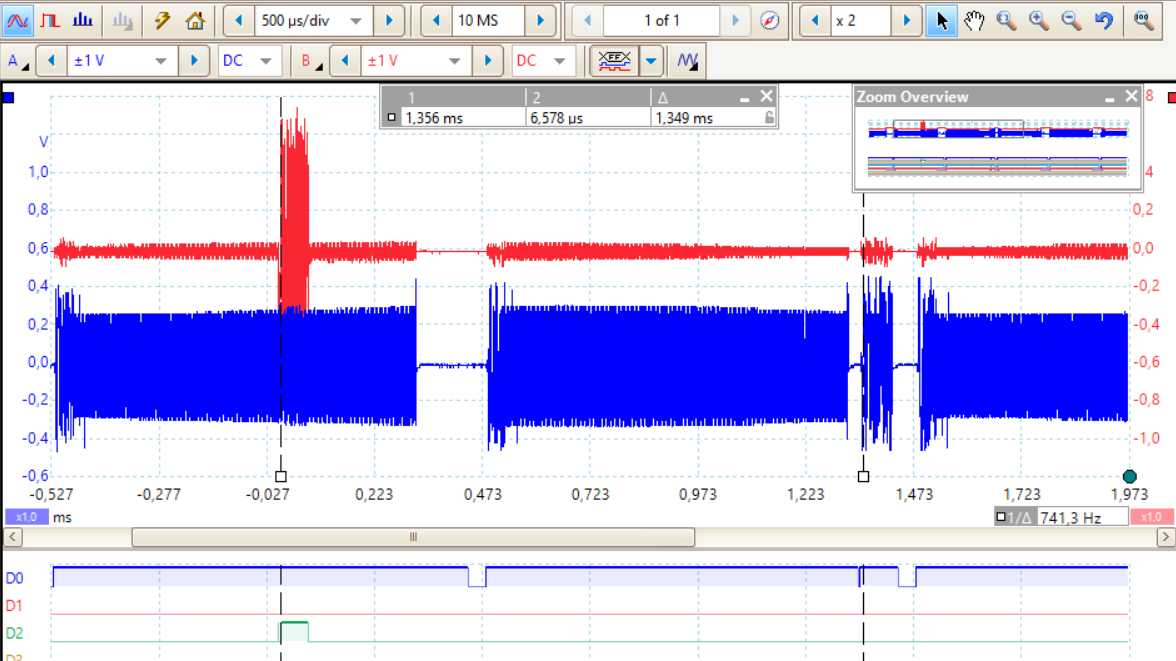

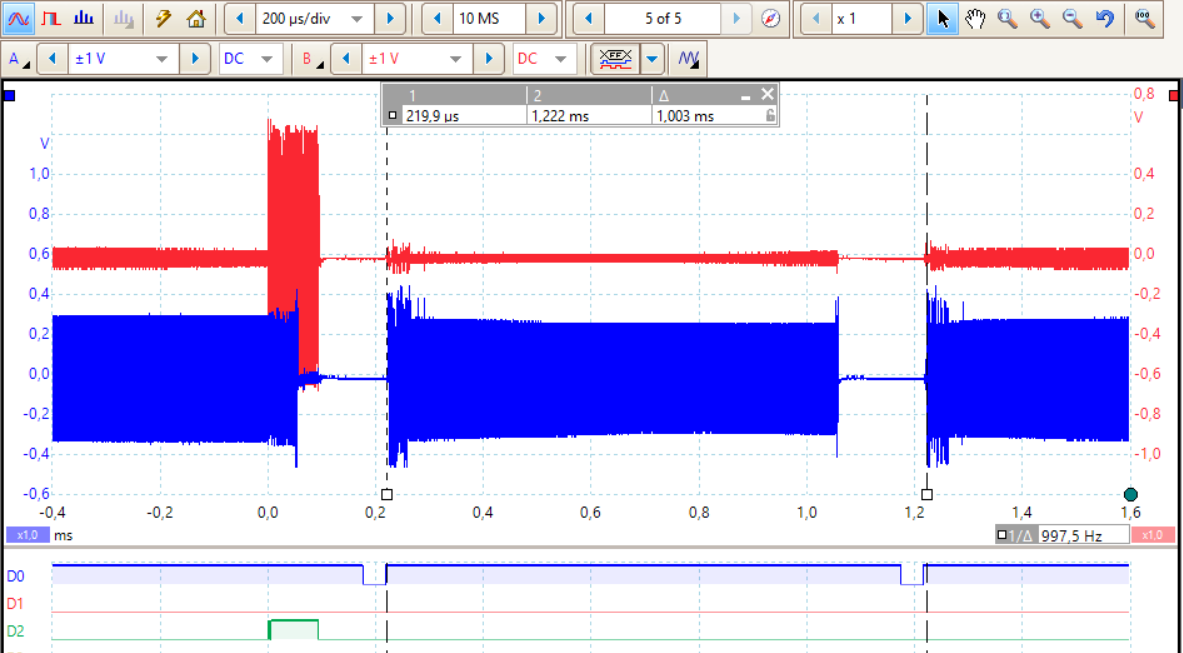

The following scope view shows a for example ARP or also a ping telegram and its answer during transmission of measurement telegrams:

Image: Scope ping telegram

This image shows a ping request (red, left cursor) and its answer (on right cursor). The ping is embedded in a currently transmission of value telegrams of 500 words (1000 byte) in a cycle of 1 ms. The gap between this value telegrams allows other short telegrams between, as shown by the ping answer, as well as of course the necessary ARP telegrams. This telegrams are typically short (lesser than 100 µs inclusively the necessary gap). Hence it possible to regarded them in the whole timing.

7.4. Scope view of meas command telegrams inside currently data transfer

As you see here, the received command telegram comes during the transmitted telegram, or after it. This is accidently. There is a only one proplem: If the command telegram arrives the Controller, and yet in this moment (only for a few microseconds) the controller programs its SPI connection newly, the command telegram is not recognized. This command telegram is then lost. But usual a command telegram can be lost, the command should be repeated by the users software as it is familiar for UDP data connection.

Because the command telegram does not need an answer, the answer is the currently running measurement telegrams, no further telegram is transmitted form the controller-meas system.

7.5. Details of software

It is described in SpeA-ControllerSw.html#ExmMeasData

8. Electrical conditions for SPE plugs

8.1. SPE Jacks, polarity

The SPE plugs of the SPE card are standard Harting jacks with two poles for SPE. If you want to connect other jacks, or harting plugs with more pins for power, you can connect it outside the card (maybe mounted above), you can use two soldering points for the SPE signals.

The polarity is primary not defined. The FPGA contains logic to detect with the SFD (Start Frame Delimiter) bit whether the polarity is reversed, and correct it. But the polarity should be well defined especially for PoDL (Power over Data Line), see chapter Power over Data Line (PoDL)

8.2. Potential isolation, ground and shield

Generally the SPE card is accomplished to the standards of the physical layer. It means shortly potential disturbance of 1.5 kV is possible, and general a potential isolation is given with filtering of disturbances.

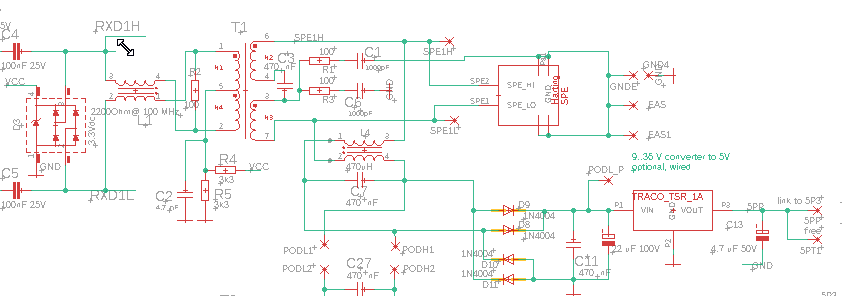

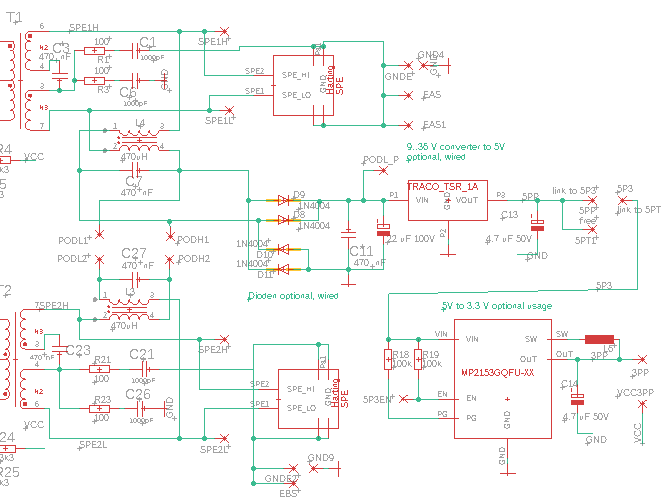

Look on this part of the schema:

Right side you see the SPE plug. It has the two SPE pins and a shield. The shield can be connected to the ground of the card using the GNDE-GND4 connection. This is recommended if the SPE card has no other Ground connection, all inputs are potential separated and the grounding of the SPE-card should be done with the shield.

It is not recommended to connect ground and shield if the SPE-card has an own ground connection for example with the cubicle ground or any other ground for due to the connected controller hardware. Two ground connections using really earth connection of via capacitors can force circular currents through the shield. That should be prevented.

Hence it is a carefully descision using the ground bridge depending on the whole wiring situation.

The middle point of the potential isolation transformer is connect with 100 Ohm and 1000 pF/1.5 kV to both the shield and the ground. This should be grounded spikes which are symmetrically on both SPE data lines. The absence of this grounding can lead to higher voltages, which are then passed through on the secondary side, of the potential isolation transformer, to the electronics. It is also a question whether this grounding should connect to the shield or to the ground of the electric circuit. If the shield is connected to ground, it is the same. If the circuit ground is connected to any earth, it is sufficient. But if the circuit ground is potential isolated, and only capacitive connected to any earth, it may be better to remove one of the resistor or capacitor to ground from the card.

Both windings to the primary mid point of the potential isolation transformer are not galvanic connected, instead by a capacitor 470 nF/100 V due to the possibility of Power over Data Line.

The mid of the secondary side of the signal transformer is grounded with 4.7 nF recommended by the manufactor (Würth). Additionally it has a middle voltage of 1.65 V, which is necessary as middle voltage for the difference inputs of the FPGA, and also for the current source output, see chapter Current source for Transmit.

On the secondary side of the potential isolation the 100 Ohm resistor for line terminating is connected. After this a so named "common mode choke" is used. This common mode choke has two reasons:

-

1) As recommended, suppress remaining common mode signal parts from differential inputs. That are possible by parasitic capacitances of the potential isolation.

-

2) Symmetric of the currents which are driven by transmission comming left side from current sources. See chapter Current source for Transmit.

Last not least a so named TVS Diode as voltage protection for the FPGA inputs is used.

The both signals after the common mode choke parallel to the TVS diode goes immediately then to the differential input of the FPGA. Alternatively for transmission there are driven from the current source left side of the 100 nF capacitors, chapter Current source for Transmit.

8.3. Power over Data Line (PoDL)

The capability to use the two data lines for power supply is one of the benefits of SPE. Usual for "Power over Ethernet" different twisted pairs are used for the power which are isolated one by another because of its own signal transformers. But in SPE there is only one pair and one signal transformer. So a capacitor in the mid point of the both primary winding of the signal transformer separated direct voltages on the line. The PoDL is defined as direct voltage in range of 12V, 24V or 48 V due to several industry standards and automobile. Because 24 V is the widely used industry standard for auxiliary power supply, this is prioritized first.

The power consumption and hence the current should be till 4 A for some applications. But such an high current needs large inductance and also resistor losses of the cables. To figure out a reasonable compromise, the standard assembly allows a max. current of no more as 0.7 A using decoupling chokes from Würth: 744870471 https://www.we-online.com/catalog/datasheet/744870471.pdf. A shortly higher current till 1 A is not an extrem problem. With this values, regarding an undervoltage of 19 V, a power transmission of 13 W is possible. Because a typical small microcontroller circuit needs power in range of 1 W for the board, it is sufficient. But is it too little to supply, for example, a circuit breaker.

Secondly, the ring structure forces that the whole current of all consumer passes all chockes, whereby two chokes are in series per SPE card. The resistance of a winding of this choke is 1 Ohm, max. 1.2 Ohm per Winding. It means one card has 4..5 Ohm. It means if you use 5 cards in the ring, it is 18 Ohm, and the last sink consumes the whole power, furthermore 12 V loss is accepted over the line, you can feed the 0.6 A, but you get only approximately 7 W on the last station. This may be enough for some approaches, but not for all.

If you need more power, the following solutions are possible:

-

a) For a only experience solution, use own power supply if you need more power.

-

b) You can deactivate the assembled chokes by open the connection between both sides (J3, J4), and use instead larger chokes mounted manually beside the card. That chokes can be connected on the soldering points J10 and J11.

-

c) It may be recommended to user extra power supply with one SPE cable but with special power wires. This is a recommended solution from the producer Harting for higher power consumption. It can be recommended also in power ranges greater 10 W. For a professional prototype solution you can mount such jacks beside the card and use also the soldering points J10 and J11.

As you see the given solution is for less power consumption < 10 W or in range of 1..2 W per station, but for prototyping an adaption to other solutions is possible.

8.4. Power supply for the card and for a connected controller card

It seems to be recommended to use the PoDL for the SPE card itself and also for the connected controller card. Expectable power consumptions are in range.

There are two solutions:

-

a) Isolated ground, use the power supply on card with max. 5V/1A

-

b) Your card has an own grounding. Then you must not use the internal power supply which is not potential isolated. You can connect your own potential isolated DC/DC converter.

The application a) may be often usable. The earth connection may be given by the shield of the SPE cable, the circuit itself is hence near the earth, but not connected to earth immediately in the station. Measurement points may be potential free by itself, for example hall-effect current measurements or measurements after a potential isolated current measurement transformer. It is a topic of capacitive coupling to the environment. Parasitic capacitive currents from the environment flows from the ground to the SPE shield, and then to the earth in that station which has the earth connection from the shield. It means the SPE cable shield gathers all parasitic ground currents. In a disturbing environment you can also box your controller and SPE card in a shield, which is not connected to your ground, but connected to the earth in the cubicle. Hence the influence from the environment or grounded in the cubicle and does not reach your controller board. Then a) is also sufficient.

The image above shows an example for a potential separated current measurement transformer on a controller with SPE card, but with isolated ground, which is housed in an own shield. The circuit itself is shielded, and hence disturbances are grounded with the shield, as a faraday cage. But less disturbance can come over the wired plugs, and in this case over the lesser shielded transformer secondary winding itself. It is of course better to shield the lines too locally grounded, and use so named "feedthrough capacitors", but this is an example to explain the problem. This lesser disturbance current flows over the circuit ground to the connected SPE cable shield, and last not least to the earth on another station. Now it is a question of amount of this disturbance current.

As you see an own isolated ground in a station grounded via the shield is often possible. You should regard other shielding approaches for your station.

The approach b) is the standard for such solution: Potential separated PoDL preparation and a locally grounded ground connection. But for the approach b) you should also think about the shield-ground connection of the SPE cable, see chapter Potential isolation, ground and shield. Do not create currents in loop over the shield!

For the approach a) which is also often sufficient for experience, the SPE card contains a 24 V to 5 V stepdown converter type TSR 1-2450 https://www.tracopower.com/de/deu/model/tsr-1-2450. The minimum input volatage for that is 6.5 V. It means PoDL for 12 V nominal voltage is also possible. The maximal input voltage is 36 V, which is proper for the recommended 24 V nominal supply voltage for PoDL.

Also a 5V to 3.3 V Stepdown converter is part of the SPE card: MP2153GQFU-33-P https://www.mouser.de/datasheet/2/277/MP2153-1624349.pdf. This can be used also for independent (or potential separated) power supply from an independent 5 V source, not from the internal TRACO power.

Last not least you can get both the 5V and also 3.3 V power supply independent of the solution on the SPE card. Look on the wiring possibilities:

As you see also in the image above: There are four diodes for a bridge rectifier. This is not for AC current on the PoDL line, it is for secure the polarity. But if the polarity is clarified (one SPE wire is minus, the other plus), then you need only one diode (recommended) as polarity protection, and a ground wire instead the minus-diode.

The TRACO power TSR-1-2450 is right side of the diodes,

it may be removed (manual soldered anyway) if it is not used.