Note: This documentation is started in German, but some parts are then written in English. As for many technical documentations, English should be used as a whole. …Replacing step by step

1. Anspruch

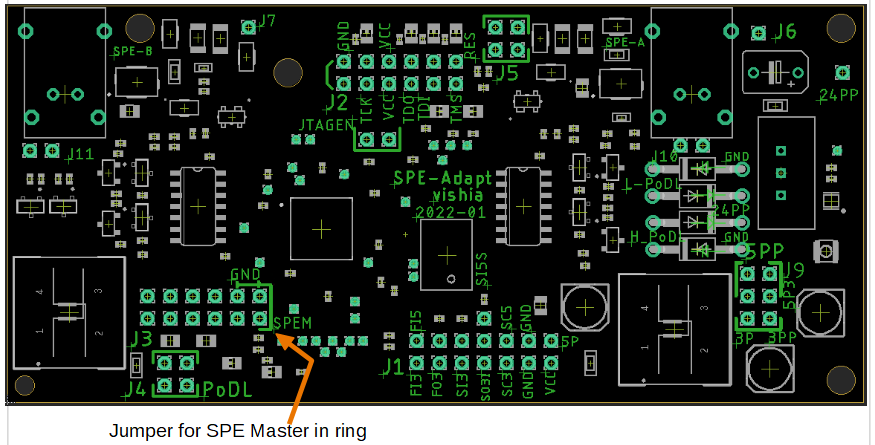

Das Board enthält zwei SPE-Anschaltungen für Ringtopologie oder Multidrop und einen FPGA Lattice XO2-4000HC zu Realisierung der Kommunikationsanbindung über SPI an einen Controller.

2. Ausgangstreiber für die Ethernetsignale

2.1. FPGA nur mit Widerstandbeschaltung vorgeschlagen für LVDS und ähnliche ist nicht geeignet

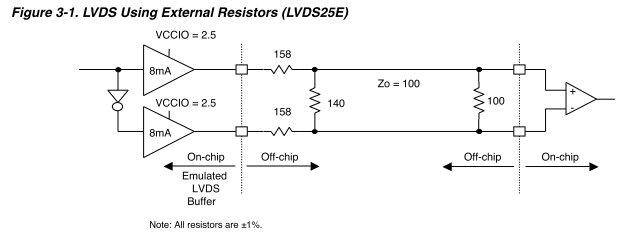

Das FPGA ist für Applikationen mit Twisted-Pair-Verbindungen mit Differenzaus- und Eingängen vorgesehen: LVDS, BLVDS, LVPECL. RSDS, siehe Lattice-Handbuch. Im Handbuch wird dafür folgende Schaltung für LVDS aufgeführt, die anderen Varianten sind ähnlich:

Das FPGA hat Differenzeingänge, die im Bereich 0.3..3.0 V mit Gleichtaktaussteuerung funktionieren und auf wenige mV Differenz reagieren. Die Ausgänge sind jedoch einfache Binärausgänge mit den üblichen Konditionen für CMOS, Strombelastbarkeit 8 mA (muss programmiert werden, ca. 4 mA als default), Ausgangstransistoren in Sättigung.

Die Differenzleitung (twisted) benötigt einen Abschluss von 100 Ohm. Das ist in der obigen Schaltung problemlos für den Eingang. Am Ausgang wird das erreicht per Spannungsteiler. Rechnerisch ergeben sich mit einer Ausgangsimpedanz der Ausgänge selbst ebenfalls etwa 100 Ohm. Jedoch ist aufgrund des Spannungsteilers der Differenzsignalpegel gering. Im Handbuch werden 350 mV angegeben. Ob eine einfache Reihenschaltung ca. 47 Ohm in Serie zum Ausgang für die Schwingungsdämpfung der Leitung auch funktionieren würde; man würde hier einen Signalpegel von ca. 1.5 V erreichen, den Abschlusswiderstand am anderen Ende einbeziehend, ist nicht näher betrachtet. Diese Lösung fällt schon deshalb aus, weil die Leitung bidirektionell betrieben werden soll. Die Ausgänge sind dann hochohmig zu schalten. Auch ist in dieser Schaltung beim bidirektionalem Betrieb 140 Ohm wirksam statt der notwendigen 100 Ohm.

Daher ist diese Schaltung für die SPE Verbindung nicht anwendbar. Sie ist geeignet für unidirektionale lokale Verbindungen (kürzere Leitungslängen) ohne Potenzialtrennung zu anderen Geräten wie angegeben über die LVDS etc. Standards.

2.2. Prinzip Stromquellen

Für den Ausgang auf die Leitung mit 100 Ohm beidseitig abgeschlossen ist eine Stromeinspeisung ideal. Hierbei wird der Abschlusswiderstand nicht beeinflusst (Idealfall). Mit Abschaltung der Stromquellen ist das Leitungsende unmittelbar als Eingang nutzbar.

Geschaltete Stromquellen (ein/aus/Richtung) haben den Nachteil, dass das Schalten selbst ein Delay hat, es muss hier mit < 10 ns gearbeitet werden. Besser ist es, einen Konstantstrom dauerhaft (abschaltbar) zu erzeugen, der dann umgeleitet wird entweder auf das Kabel oder auf eine Spannung zum Abfließen. Die kann beispielsweise mit Dioden entkoppelt werden.

Eine Recherche über passende Schaltkreise oder Schaltungen brachte aber keine brauchbaren Ergebnisse.

Die andere Möglichkeit ist, den Strom über Opendrain bei Bedarf auf Masse fließen zu lassen oder bei abgeschalteten OpenDrain eben in das Kabel. Dabei ist jeweils eine Leitung im Kabel auf Masse terminiert (über Open Drain), das andere Leitungsende liegt an der Stromquelle. Der Leitungsabschluss ist damit hochohmig, und nur vom 100 Ohm terminiert, da immer ein Ende hochohmig ist und die Gesamtschaltung ist symmetrisch potenzialgetrennt zum Kabel.

Wenn vorausgesetzt werden kann, dass es keine oder sehr wenig Einfluss zwischen den Wicklungen gibt (in diesem Fall kapazitiv), dann darf eine Leitung wechselweise einseitig terminiert werden, auf der anderen Potenzialseite, also an der Twisted Line, ist dies nicht sichtbar.

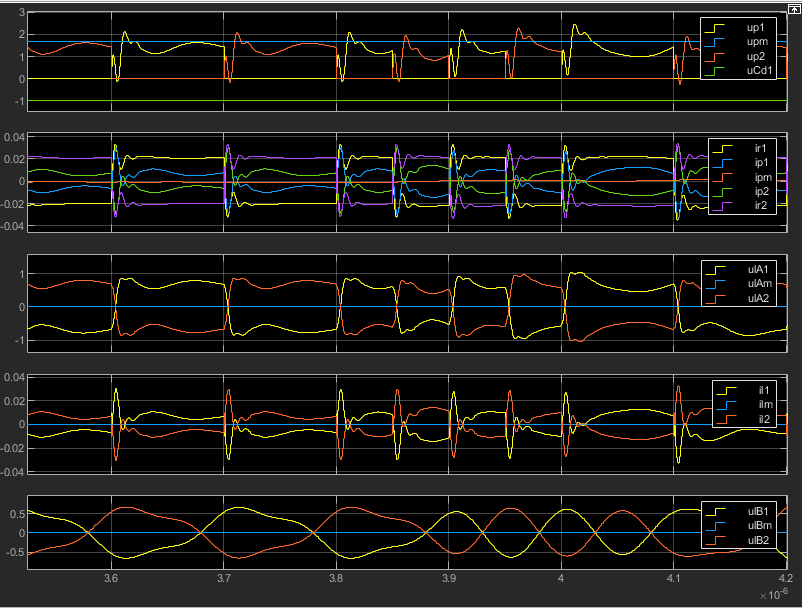

Mit dieser Voraussetzung wurde folgende Schaltung gefunden, hier zunächst als Simulink Modell präsentiert, das auch zur Simulation und zur Funktionsüberprüfung diente:

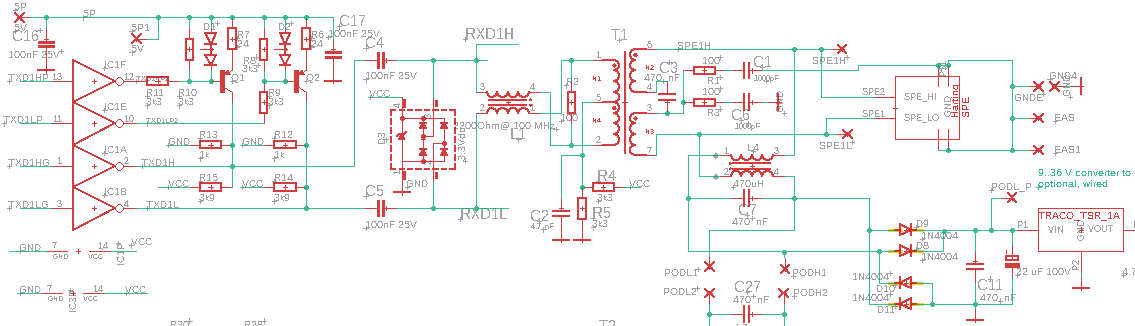

Links im Bild ist eine Testansteuerung realisiert, die einige 100 ns und 50 ns-Impulse erzeugt, wie sie in den Scope-Bildern sichtbar sind. Das Ausganssignal geht direkt und negiert auf ein MOSFET in Open-Drain-Schaltung. In der Realisierung der Karte ist dies je ein Gatter eines 74LVC06AD (Nexperia), ein open-drain Hex Converter, on/off Switch-times < 3 ns.

Von oben wird ein Konstantstrom eingespeist, über Simulink-Stromquellen, 20 mA. Die darüber liegende Spannungsquelle 4 V mit Diode dient einerseits dazu, die Ausgansspannung auf 4 V + Diodendurchlassspannung zu begrenzen, wirksam bei reverser Stromrichtung. Es führt auch dazu dass die Stromquelle auch in der Simulation bei > 4.7 V "verhungert", also keinen Strom mehr treibt. Die adäquate Schaltung auf dem Board sieht wie folgt aus:

Die Stromquelle wird von Q1 und Q2 gebildet, mit konstanter Basisspannung zu 5P über die Doppeldioden D1, D2. An den Emitterwiderständen bildet sich damit ca. 0.6 V, mit 24 Ohm bildet sich ca. 20 mA. Die Spannung GND zum Kollektor kann bis zu ca. 4.8 V betragen (Restspannung UCE dann 0.2 V), danach verringert sich der Strom auf 0. Allerdings begrenzt zuvor die TVS Diode 710-824012823 (Würth) die Spannung auf ca. 3.3 V. Dies betrifft nur Schaltspitzen.

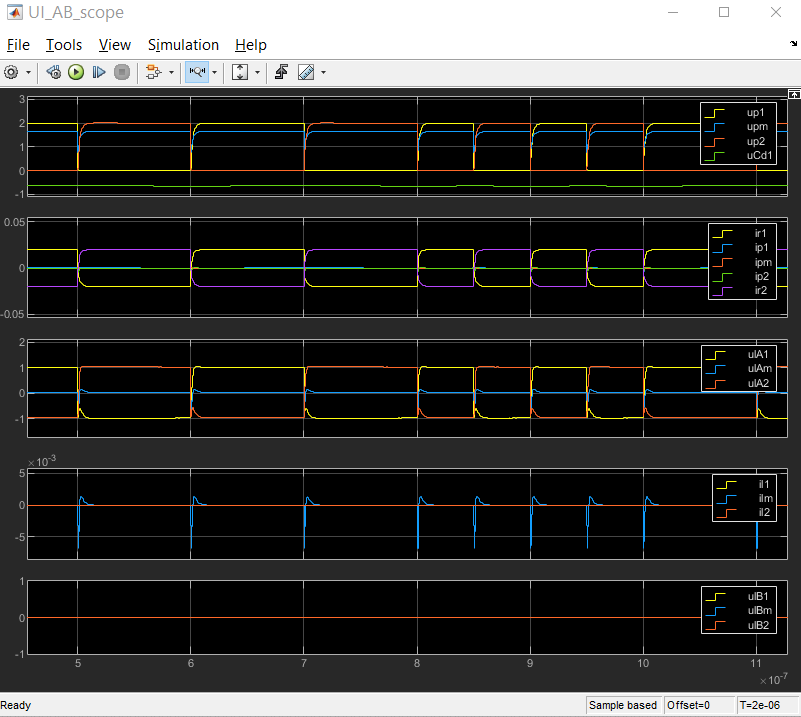

In der folgenden Scope-Ansicht ist das Kabel noch getrennt. Ebenfalls die Entstördrossel ist überbrückt, nicht wirksam. Damit ist das Verhalten zunächst überschaubarer:

-

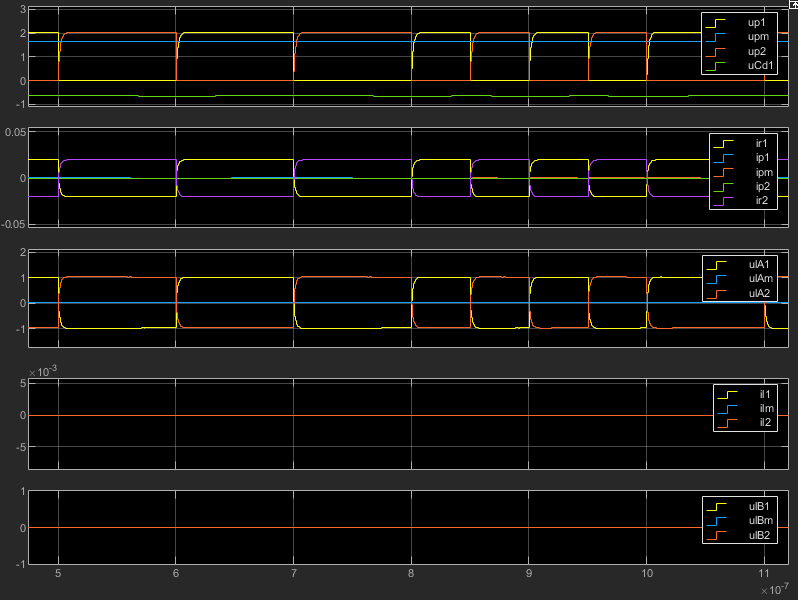

Track 1 zeigt die Ausgansspannungen an der Stromquelle/Open drain. Die Spannung stellt sich auf 2.0 V ein, dies entspricht dem Spannungsabfall über den Terminierungs-Widerstand bei 20 mA. Im Übergang gibt es eine kapazitive Last der Stromquelle. Das ist einerseits die Ausgangskapazität an den Open-Drain-Schaltern, im Simulink mit 20 pF angegeben. Zum zweiten ist für den Übertrager 2 mal 7 pF Wicklungskapazitäten zwischen Primär- und Sekundärwicklung angegeben.

-

upm im Track1 ist die Spannung an der Mittelanzapfung. Diese ist mit Quellenwiderstand 1.65 kOhm auf 1.65 V eingestellt. Das bestimmt die Mittelspannung bei abgeschalteten Stromquellen für die Empfangsrichtung. Eine Auslenkung der Mittelspannung (ohne C) ist sichtbar. Die Terminierung über C ist in der Simulink-Schematik für diese Messung weggelassen.

-

Track 2 Der Strom hat eine Anstiegsverzögerung. Die Anstiegsverzögerung ist von der Ausgangskapazität am Open/Drain und der Stromquelle hervorgerufen. Im Modell sind hier 20 pF angegeben (kleine Cs parallel zu den Open Drain). Bei 20 mA ist dies ein Anstieg von 1 ns/V, also die etwa ablesbaren 2..3 ns (Periodenbreite ist 100 ns, 50 ns = 0.5*10-7 laut Scope-Bild).

-

Track 3 ist die Spannung am SPE-Plug. Über den 100 Ohm Terminator auf der Innenwicklung stellen sich auch hier ca. 1.0 V (2.0 V Differenz) ein. Es ist nichts angeschlossen, daher ist die Ausgangsspannung dopppelt hoch.

-

Track 4 und 5 ist die Gegenseite der Leitung und hier nur mit kleinen Störsignalen behaftet.

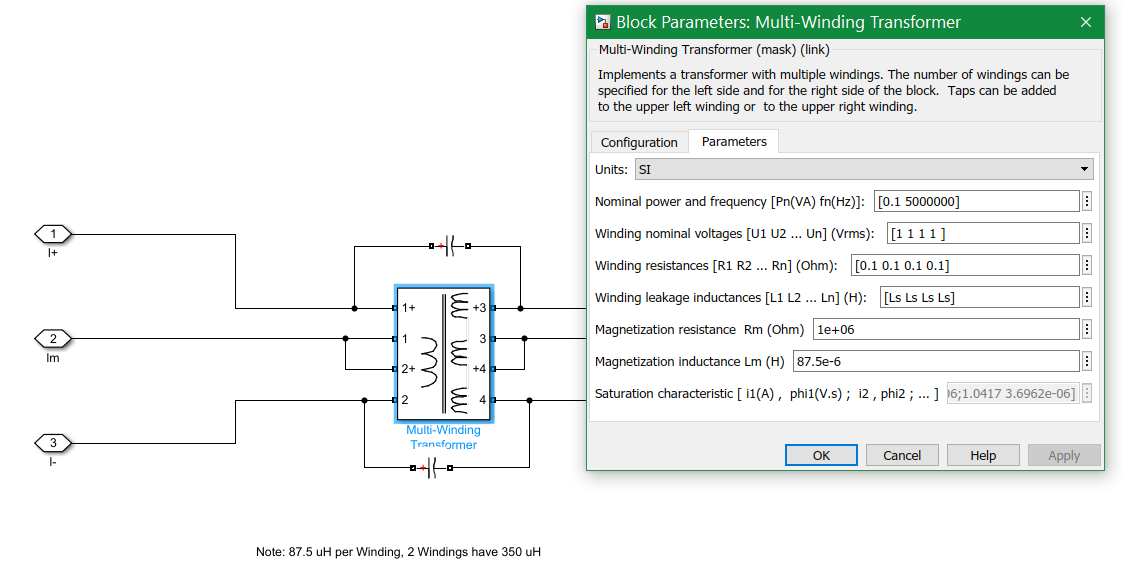

Der Übertrager ist mit 350 µH Hauptinduktivität (87.5 µH pro Windund) und 30 nH pro Windung Streuinduktivität angegeben. Das ist ca. 1/5000. Leider ist dieser Wert für dieses Bauteil in den Datenblättern nicht genau angegeben. Die Information 60 nH gemessene Streuinduktivität stammt aus einer Messung Würth-intern Mail von Markus Thoss, Würth-Elektronik an Dr. Schorrig vom 18.12.2020 10:56. Ebenfalls in der Simulation wurde eine Querkapazität zwischen den Wicklungen zwei mal 7 pF eingebracht (laut Aussage aus Mail insgesamt 10 bis 15 pF).

Im Bild irritierend, es sind drei Wicklungen rechts dargestellt, das Bild in Simulink ist aber konstant und zeigt nicht die Parametrierung. Die Anschlüsse stellen die Verhältnisse richtig dar, je 2 Wicklungen primär und Sekundär. In Simulink wird nicht die Windungszahl angegeben, sondern intern mit der Leistung und Frequenz berechnet. Solche Trafos sind eher für 60/50 Hz gedacht, Leistungen im Megawattbereich. Sie funktionieren aber mathematisch, daher auch wie hier angegeben bei 5 MHz (100 ns Pulslänge) und 0.1 VA.

Parmetrierung außen Ls = 30e-9 und Cs = 7e-12 (beide Kapazitäten).

Die gleiche Simulation aber mit CommonModeChoke und kapazitiver Terminierung der Mittelanzapfung sieht wie folgt aus:

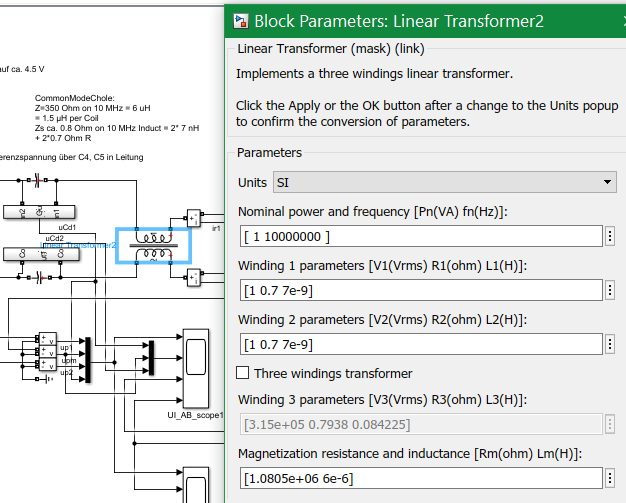

Die Spannungen up1, up2 an der Stromquelle sind nur beim genauen Hinsehen etwas größer als 2.0 V, aufgrund des Innenwiderstands der CommonModeChoke. Diese ist mit 7 nH Streuinduktivität pro Windung (14 nH wirksam) parametriert, die Hauptinduktivität beträgt 6 µH. Diese Daten sollten der Datenblattangabe von 744232222-1721301.pdf (we-online.de) entsprechen.

Interessant ist es, dass mit diesen beiden Maßnahmen der Impuls an der kabelseitigen Mittelanzapfung weg ist. Die Gleichtaktunterdrückung funktioniert (wie zu erwarten).

2.3. Kabelwirkung in der Simulation

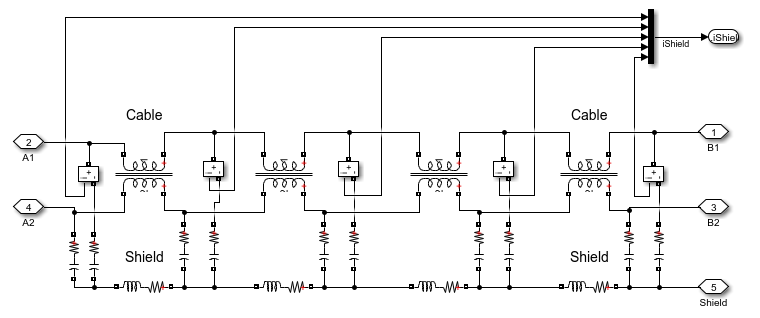

Das Kabel wird mit folgender Schaltung für die Simulink-Untersuchung nachgebildet:

Die Nachbildung erhebt nicht den Anspruch einer genauen Kabeluntersuchung sondern soll nur in etwa die Wirkung des Kabels demonstrieren. Als Parameter des Kabels ist für die folgenden Untersuchungen folgendes eingestellt:

Das LsCable = 5 µH ist die Steuinduktivität zwischen den parallelen Wicklungen auf eine Wicklung bezogen. Die Kabelinduktivität ist als 10 µH insgesamt. Das würde ca. 600 Ohm Impedanz bei 10 MHz entsprechen, wenn diese Induktität punktförmig wirken würde. Der Spannungsabfall ist aber auch in der Simulation mit dem einfachen Kabel erheblich niedriger. Das liegt daran, weil eben die Einzelelemente miteinander wirken und die Induktivität verteilt ist. Die Wicklung selbst ist jeweils mit 30 uH pro Segment als Hauptinduktivität der für die Kabelsimulation genutzten Transformatoren angegeben (Summe 120 µH pro wire), was etwa 40 m eines ausgedehnten freien Drahtes in Summe entspricht. Dieser Wert ist aber nicht wirksam, wirksam ist die Verkopplung der Wicklungen mit der etwa 10 fach geringeren Steuinduktivität. Dies ist der Effekt der twisted pairs. Inwieweit diese Werte für einen bestimmten Kabeltyp relevant sind, ist hier nicht weiter betrachtet.

Das CsCable ist die gesamte Schirmkapazität des Kabels einer Wire zum Schirm. Eine extra Kapazität zwischen den Wires ist hier nicht angegeben.

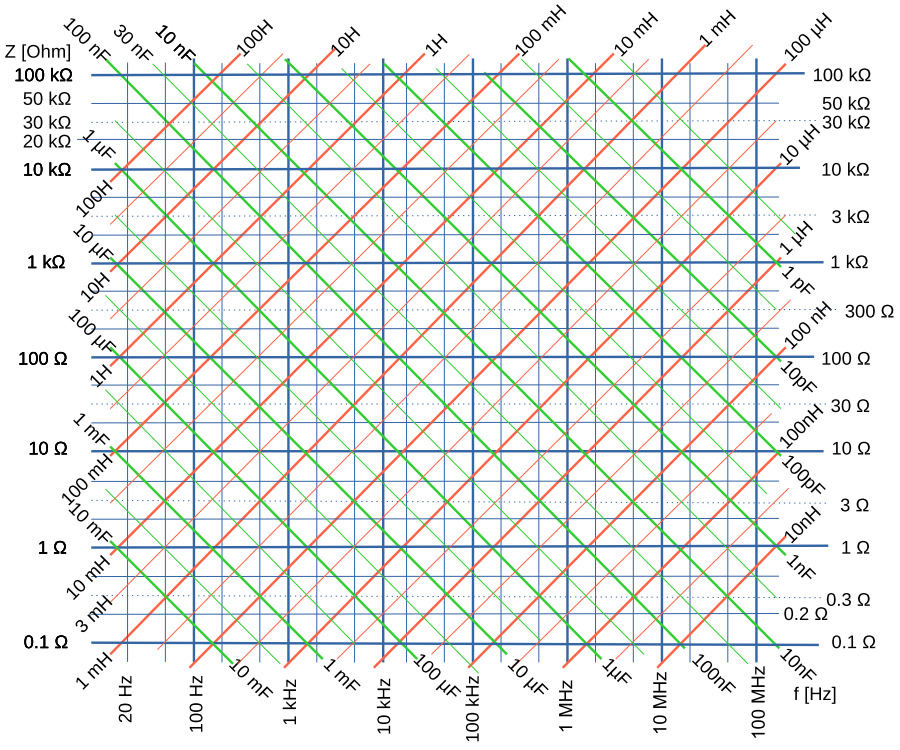

Die Impedanzen der Streuinduktität und des C eines Wire liegen bei einer Frequenz von f=1.6 MHz (genauer 10 MHz/2*pi) auf dem gleichen Wert von 100 Ohm. Damit ist der Wellenwiderstand des Kabels wie erforderlich 100 Ohm, mit dieser einfachen Kabelsimulation.

Mit diesem Kabel ergibt sich ein Signalverlauf, einschließlich CommmonModeChoke und kapazitiver Mittelanzapfung wie im Vorkapitel beschrieben. Dabei ist wie im Nachfolgekapitel beschrieben die Gleichspannungstrenn- C4 und C5 auf eine Spannung von 1.01 V eingestellt, C2 hat 1.65 V. Das Einschwingen dieser Kondensatoren wird im Nachfolgekapitel behandelt.

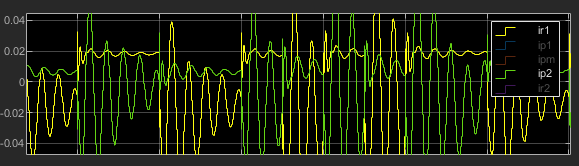

Gegenüber dem Bild ohne Kabel zeigt der Strom in Track2 ein Einschwingverhalten mit ca. 100 MHz nach jeder Umschaltflanke. Beim Strom direkt in das Kabel, Track 4, fällt auf dass es zu Anfang einen Strompeak über 20 mA gibt, der dem Umladen der Kabelkapazitäten dient bzw. davon verursacht wird. Der Strom im Kabel schwingt mit ca. 15 MHz und liegt im Bereich 5..10 mA. Hier dürfte die Kabelinduktivität mit den verteilten Kabelkapazitäten die entscheidende Rolle spielen.

Am anderen Ende kommt ein brauchbares Signal an, mit deutlichen phasenrichtigen Nulldurchgängen, aber insgesamt gerundet von den Übertragungszeitkonstanten. Der Wechsel zwischen 100 ns Pulsbreiten und 50 ns der Manchester-2-Codierung wird deutlich getragen. Auffallend ist allerdings die Laufzeit im Kabel. Die kurzen Impulse fangen ca. 80 ns später beim Empfänger an.

In der Simulation wurden einige Messungen mit Modifikation der Kabeleigenschaften gemacht. Es wurde beobachtet, dass beispielsweise eine 10 MHz Schwingung aufschwingt, (50 ns Pulse) wenn die Kabelkapazität geringer ist bei gleicher Induktivtät etc. Der stabile Betrieb wird tatsächlich erreicht, wenn die Impedanz beider Komponenten bei 10 MHz gleich ist (Resonanzpunkt) und der Terminierung von 100 Ohm entspricht.

Damit wird das Prinzip gezeigt, auch dass die Simulation in Simulink brauchbare Ergebnisse berechnet. Welche Kabellänge eines Standard SPE-Kabels dem entspricht, ist hier nicht näher untersucht.

Eine kleine Hilfsgrafik.

2.4. Gleichspannungpegeltrennung / Verhinderung von Gleichstrom im Trenntrafo, C4, C5

Die ursprüngliche Intension von C4 in Reihe mit einem Stromausgang war die Verhinderung eines Gleichstromanteils durch den Trenntrafo T1. Dieser kann entstehen durch Toleranz der beiden Gleichstromquellen oder auch durch ungenaue 1:1 Verhältnisse der Pulse. Letztere entstehen trotz gleichspannungsfreier Manchester-2-Codierung dadurch, dass die Pulsweite gelegentlich auf 90 ns gekürzt oder auf 110 ns erweitert wird (im Synchronisations-Vorspann) zwecks Synchronisierung der Taktlage von empfangenem Signal zum internen und Sendetakt.

Die Höhe der damit entstehenden Gleichströme ist < 2 mA für <10% Toleranz der beiden Gleichstromquellen gegeneinander bzw. sehr viel kleiner für gelegentliche Pulsverschiebungen. Der Arbeitsstrom im Trenntrafo ist ca. 20 mA. Allerdings steht die Höhe des Arbeitsstromes nicht in Relation zum Gleichstrom, da der Arbeitsstrom entgegengerichtet auch in der Sekundärwicklung fließt uns sich daher magnetisch aufhebt, ausshließlich der geringen Streuung beider Wicklungen gegeneinander (<0.1%). Es ist also besser, einen Gleichanteil im 1 mA-Bereich zu verhindern.

Allerdings haben C4 und C5 eine weitere wichtige Aufgabe: Der Mittelunkt der Primärwicklung von T1 sollte etwa auf 3.3 V /2 liegen (1.65 V), damit ist eine gute Spannung für die Differenzeingänge gegeben. Die mittlere Spannung der Stromausgänge pendelt sich dagegen auf ca. 0.5..0.8 V im Betrieb ein. Ohne C4 und C5 würde diese Spannung die Spannung am Mittelpunktskondensator C2 bestimmen.

Mit C4 und C5 wird die Mittelpunktspannung vom Spannungsteiler R9, R10 bestimmt auf 1.65 V gesetzt, C4 und C5 laden sich im Betrieb mit der Differenz von ca. 1 V auf. In einer Sendepause mit Gap im Telegrammstrom oder im Betrieb als Empfänger sind die Stromquellen jedoch inaktiv (hochohmig) geschaltet. Damit die Spannung am C4, C5 gehalten wird und nicht mit langer Zeitkonstante zufällig floatet, ist die Spannung am Stromquellenausgang durch einen Spannungsteiler mit R7, R12 bzw. R8, R13 und R27, R32 bzw. R28, R33 mit 1.0 kOhm und 3.9 kOhm auf eine Spannung von 0.65 V terminiert.

Für die Empfangsseitenbetrachtung: Hinter der CommonModeChoke (CMC) liegt damit eine Last 0.8 kOhm + 0.8 kOhm zur Masse. Diese ist unerheblich gegenüber dem Terminatorwiderstand von 100 Ohm 1.6 kOhm wirksam parallel, aber hinter der CMC), die Widerstandskombination bedämpft eher noch mögliche Schwingungen der CMC mit den Ausgangskapazitäten der Stromquellen bzw. Eingangskapazitäten der Differnrentialeingänge des FPGA.

Wenn die Gleichstromquelle Toleranzen aufweisen, dann läuft die Spannung an demjenigen Kondensator C4 oder C5 davon, bis sich die Gleichstromquellen angeglichen haben. Das ist der Fall, wenn die größere Stromquelle in Begrenzung, an die Spannungsgrenze geht. Dann ist jedoch der normale Betrieb nicht mher gewährleistet, da dann die Leitung nicht mehr mit Stromeinspeisung, sondern mit niederohmiger Spannungseinspeisung betrieben wird. Dieser Effekt muss also verhindert werden.

Dieser Spannungsteiler mit einem Innenwiderstand von 0.8 kOhm pro Stromquellenausgang wirkt als Innenwiderstand der Stromquelle. Der Strom ist also mit 1.25 mA/V bei 20 mA Einspeisung nicht konstant sondern spannungsanhängig. Dieser Effekt ist aber gewollt, er führt bei Toleranzen der Stromquellen zu einem Arbeitspunkt im Schnittpunkt der Kennlinien. Wenn beispielsweise die eine Stromquelle toleranterweise 20.1 mA treibt, dann verschiebt sich die Mittelspannung um ~25 mV, so dass beide Stromquellen sich auf 20.05 mA einstellen. Ohne diese Maßnahme würde eine der Stromquellen bis an die Begrenzung laufen.

In folgenden Bildern sind Simulationsergebnisse gezeigt und diskutiert mit entsprechenden Modifikationen der Elemente.

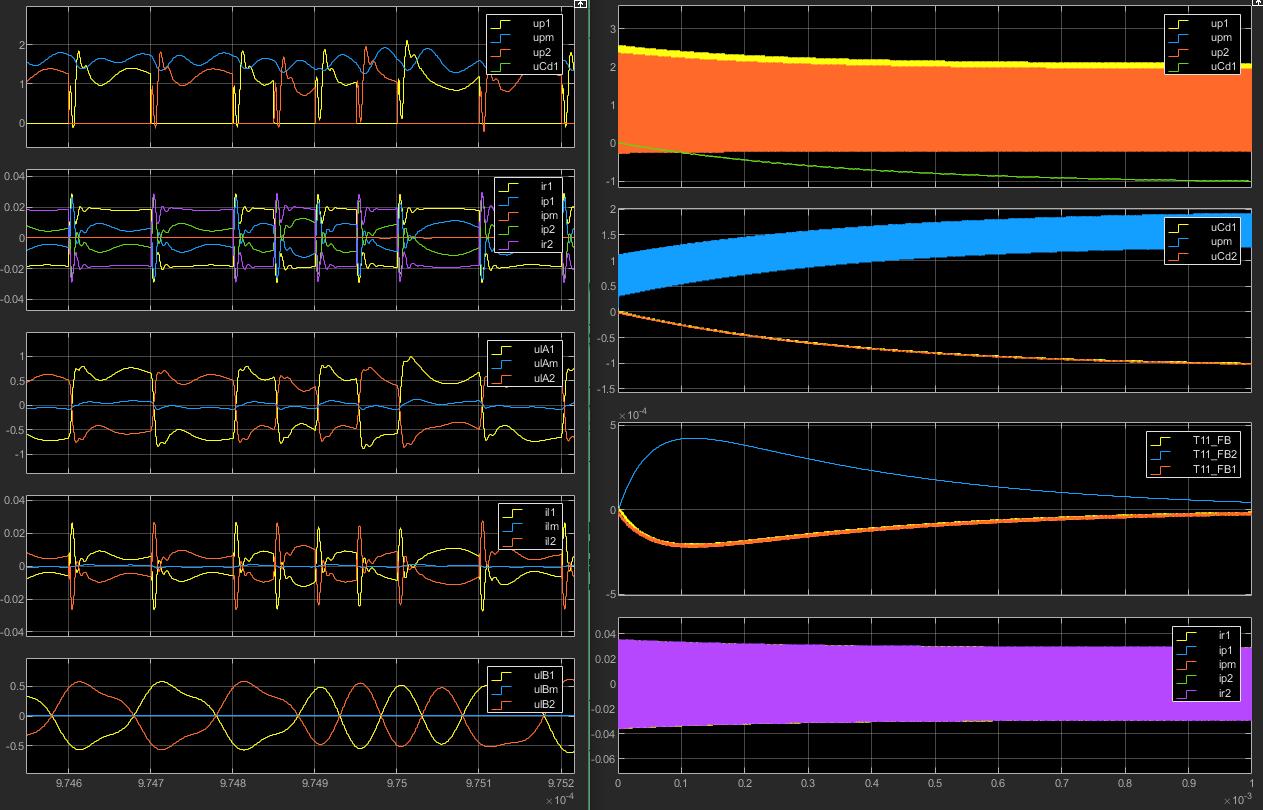

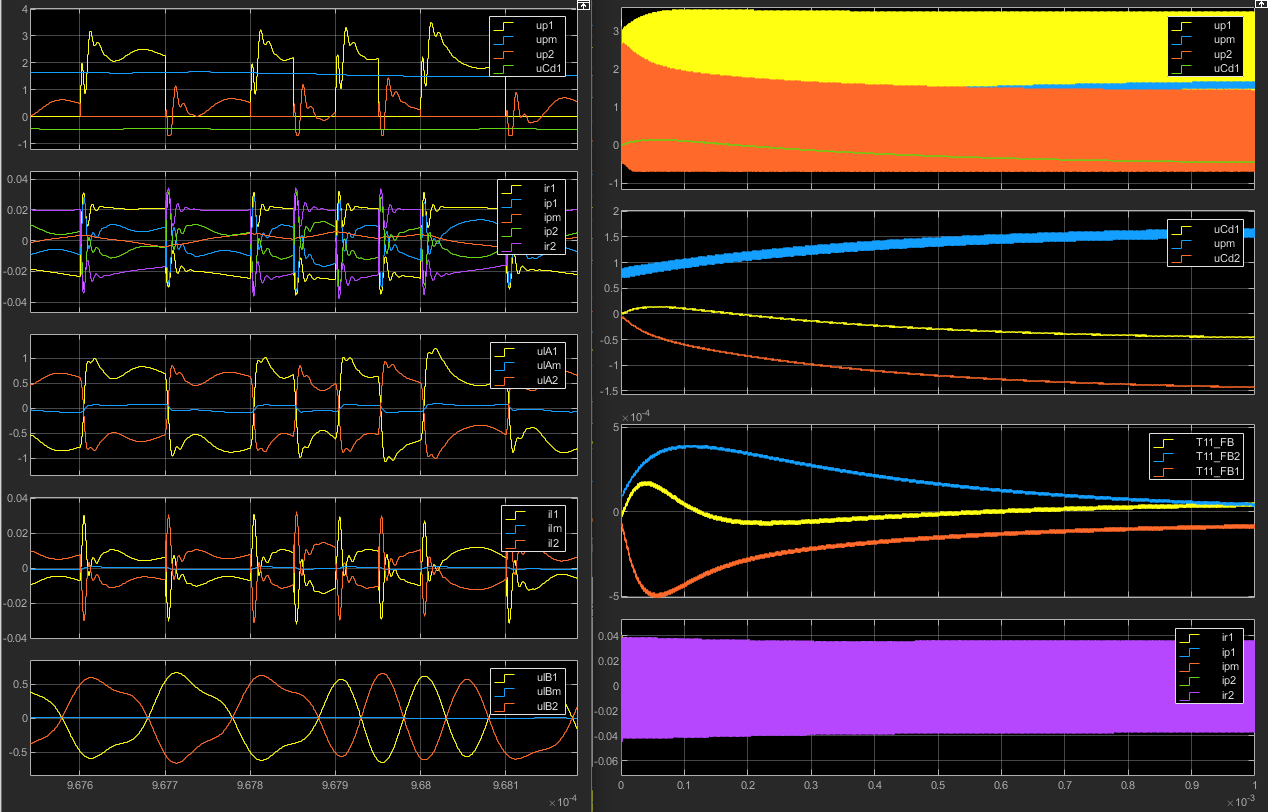

Gleiche Stromquellen, Mittelanzapfung 4.7 nF 0 Ohm

Dies ist der erwartbare Normalzustand.

Einschwingen, hier mit Startbedingung Spannung in C4, C5 =0: C4, C5 laden sich auf, innerhalb ca. 1 ms, da Gleichstrom aus R9, R10 nur max. ca. 0.4 mA (rechts, Track3, blau, Mittelwert Strom Mittelanzapfung).

Der statische Zustand nach Laden der C4, C5 ist links gezommt dargestellt:

-

Track 1: Spannungssignale an den Stromquellen schalten zwischen Gnd und der sich aufgrund Last einstellenden Spannung beim Konstantstrom. Das sind im Mittel 1 V, da 100 Ohm primär, Kabel und 100 Ohm am anderen Kabelende als Last auftritt. Die Last zeigt aber ein dynamisches Verhalten: Insbesondere nach dem Umschalten tritt kurzzeitig geringere Spannung auf, da der Strom erst noch die Schirmkapazitäten im Kabel umladen muss.

-

Track 2: Ströme aus der Stromquelle und durch die Common Mode Choke ip1, ip2 gelb und violett. Es stellen sich die eingeprägten 20 mA ein, mit kurzem Einschwingen mit ca. 100 MHz. Die Ströme in den Trenntrafo und in das Kabel ir1, ir2 grün und blau sind niedriger. Es findet eine Stromaufteilung statt zwischen Trenntrafo T1 und dem Terminatorwiderstand 100 Ohm. Das Kabel hat eine höhrere Impedanz als der sekundäre 100 Ohm Terminator, da die Kabelinduktivität noch in Reihe liegt, folglich sind die Ströme in das Kabel niedriger als in den eigenen 100 Ohm Terminator. Kurz nach dem Umschalten ist jedoch ein hoher Strom in das Kabel zu beobachten, zurückzuführen auf Schirmkapazitäten.

-

Track 3: Spannungen am Kabel. Diese spiegeln auch den Strom in den Terminatorwiderstand über dessen zeitinvariante 100 Ohm. Es ist im Mittel 1 V Differenzspannung messbar.

-

Track 4: Strom in das Kabel, wie auch im Track 2 sichtbar.

-

Track 5: Spannung am 100 Ohm Terminator am anderen Kabelende, dies ist das Nutzsignal beim Empfänger. Es zeigt sich eine Verzögerung, der Pegel ist gut nutzbar.

Wenn C4, C5 noch nicht eingestellt sind ist die Spannung an den Stromquellen höher, es ist die Mittelspannung an der Mittelanzapfung von ca. 0.6 V zu addieren, da c4 und C5 ca. noch 0 V haben. Im eingeschwungenen Zustand liegt an der Mittelanzapfung zwar ca. 1.65 V, aber die C4, C5 sind auf die gleiche Spannung eingestellt.

Die anderen Signale (Ströme, insbesondere am Kabelende) sind allerdings sehr identisch. Die Kondensatoren sind tatsächlich nur notwendig, um die Spannung an der Mittelanzapfung auf den halben Wert der Betriebsspannung für die Empfangsrichtung einzustellen.

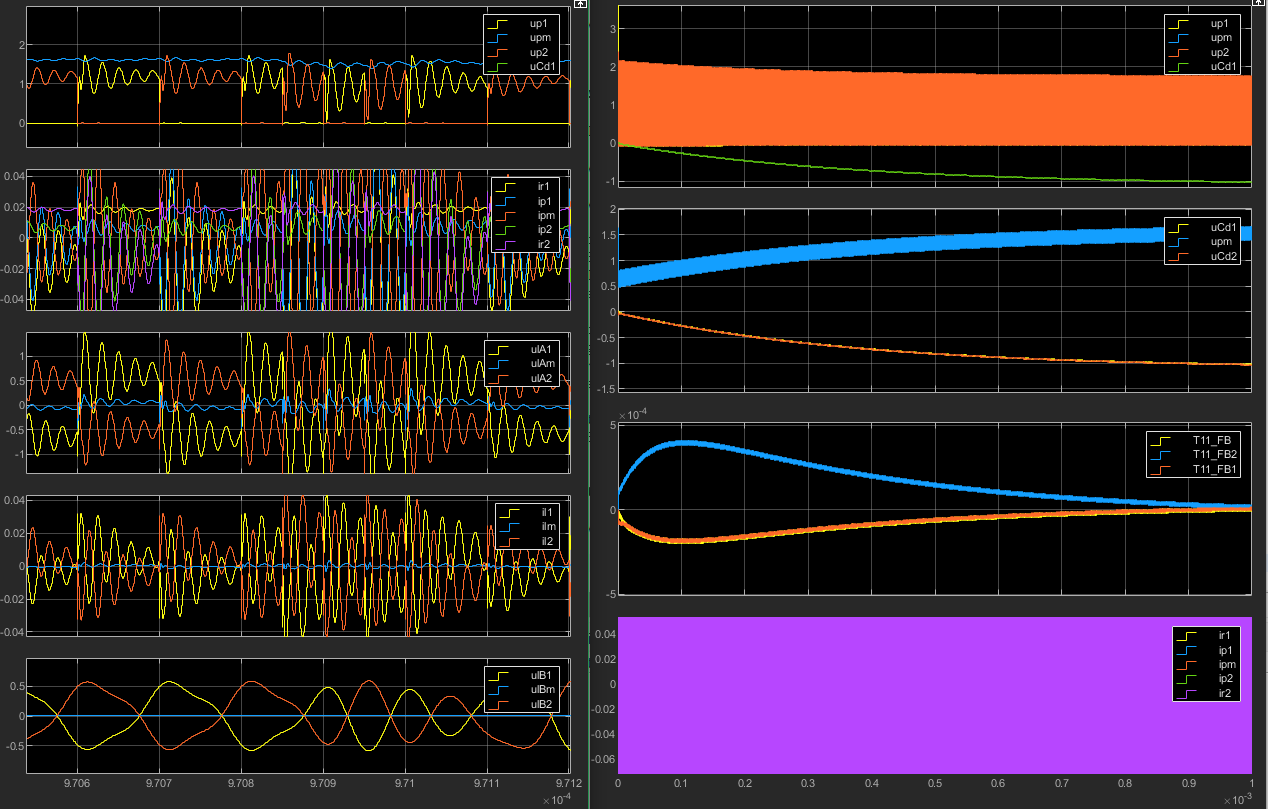

Gleiche Stromquellen, Mittelanzapfung ohne kapazitive Erdung

Die Stromeinspeisung ist nicht symmetrisch. Jeweils ein Wicklungsende des Trenntrafo T1 wird mit konstantem Strom und nicht determinierter Spannung betrieben, das andere Wicklungsende ist auf 0V determiniert durch den leitenden Open-Drain-Ausgang. Wenn diese Schaltungsanordnung nur eine Induktivität betrachtet, d.h. die Mittelanzapfung nicht verdrahtet ist, dann ist die Schaltung symmetrisch. Im folgenden Bild ist dies simuliert:

Es ist sichtbar dass links Track 1, blau upm im Mittel auf 1.65 V liegt (über Spannungsteiler Quellwiderstand 1.65 kOhm, notwendig um die Mittelspannung für den Differenzeingang zu sichern), ansonsten aber sich frei einstellen kann. Aufgrund Dynamik im 100 ns-Pulsbreitenbereich schwingt die Mittelanzapfung leicht mit einer Resonanzfrequenz von ca. 20 MHz. Zwischen den Ausgängen der Stromquelle in diesem Track up1, up2, gelb, rot liegt noch die Common-Mode-Choke, die möglicherweise zusammen mit dem Außenkabel dafür verantwortlich ist. An den Stromquellenausgängen ist eher eine etwas kleinere Resonanzfrequenz sichtbar, die wegen der Pulseinprägung aber kaum zum tragen kommt.

Die anderen Signalverläufe unterscheiden sich allerdings nicht.

Die Frage ist, woran liegt das:

Im zweiten Track links ist ipm selbstverständlich fast 0, sichtbar 0, der Gleichspannungsquellenwiderstand beträgt 1.65 kOhm. Im Bild darüber, mit kapazitiver Terminierung der Mittelanzapfung ist ein Strom sichtbar. Dies ist aber ein nicht in der Periode schwingender Strom sondern ein kleiner Strom ca. 2 mA, der eine langsame Ladungsänderung am Mittelpunktkondensator C2 bewirkt da das System der Kondensatorspannungen eben noch nicht eingeschwungen ist. Es ist kein Wechselanteil im Bereich der Pulsung messbar.

Die beiden Wicklungen des Trenntrafo sind magnetisch stark gekoppelt. Das bedeutet, ein eingeprägter Strom der einen Wicklungshälfte wird symmetrisch auf die Sekundärseite übertragen, auch dort sind beide Wicklungen gleich stromdurchflossen (symmetrische Belastung vorausgesetzt), und folglich wird der Strom aus der einen Primärwicklungshälfte induktiv in die zweite Wicklungshälfte eingeprägt. Für einen Strom in der Mittelanzapfung gibt es aus magnetischer Sicht keine treibende Kraft.

Aber der andere Spannungsverlauf an der Mittelanzapfung sollte für ein dI/dt verantwortlich sein. Es ist nun die Frage ob die Common-Mode-Choke dies verhindert.

Dazu ein Simulationsbild ohne Common-Mode-Choke:

Hier spiegelt nun die Mittelanzapfung tatsächlich den halben Spannungsverlauf an dem jeweils spannungsoffenen Wicklungsende wider, lediglich gleichspannungsverschoben wegen der 1.65 V Mittelspannung. Das ist das erwartbare Ergebnis. Die Oszillation im Bereich 20 MHz ist also tatsächlich von der Common-Mode-Choke bestimmt.

Die Ausgangsspannungen der Stromquellen sind kaum niedriger, die Common-Mode-Choke verursacht also kaum Impedanz.

Mit Mittelanzapfung-C2, ohne Common Mode Choke

Es stellt sich aber nunmehr die Frage der Verhältnisse ohne Common-Mode-Choke aber mit C2 an der Mittelanzapfung:

Hier ist mit dem Mittelanzapfungs-C und dem Kabel eine Resonanz von ca. 60 MHz feststellbar. Selbst die Spannung an C2 ist volatile, der zugehörig Strom ipm im zweiten Track ist stark oszillatorisch. Die wirksame Spannung am anderen Kabelende ist zwar dennoch brauchbar, doch diese Variante kann nicht empfohlen werden:

Die CommonModeChoke ist diejenige, die die Ströme aus den Stromquellen vergleichmäßigt. Das wird verdeutlicht, in dem im selben Scope Bild der linke Track2 ohne CommonModeChoke mit C2 die Ströme aus den Stromquellen betrachtet werden:

Wogegen der von der Stromquelle bestimmte Strom tatsächlich etwa 20 mA beträgt und nur leicht oszilliert (würde mehr konstant sein ohne R7, R8), ist der Strom in der anderen Wicklungshälfte sehr stark oszillierend. Es bildet sich ein Netzwerk mit C2 und der Leitung am galvanisch entkoppelten aber magnetisch verkoppelten Kabel. Die Ströme in das Kabel sind im Gesamtbild in Track 4 links dargestellt.

Schlussfolgerung mit CommonModeChoke und kapazitiven Mittelpunkt

Folglich gibt es zwei sinnvolle Betriebsarten:

-

Ohne CommonModeChoke und ohne Mittelpunktkapazität.

-

Mit CommonModeChoke und mit Mittelpunktkapazität.

Die Dämpfung der CommonModeChoke ist für diese Schaltung auch damit zu erklären, dass eben die CommonModeChoke für die notwendige Verkopplung der beiden Ströme jeweils einer aus der Stromquelle und der anderen zur Masse sorgt.

Da mit CommonModeChoke auch die Mittelpunktkapazität C2 verwendet werden kann und diese aus GleichtaktStörunterdrückungGründen empfohlen ist, sollte dies als Standardbeschaltung verwendet werden.

Im Layout ist allerdings ein Widerstand in Reihe zu C2 vorgesehen, der als 0-Ohm Drahtbrücke bestückt wird. Mit diesem R11 in der Bauform 0805 (manuell lötbar) ist eine gewisse Experience möglich.

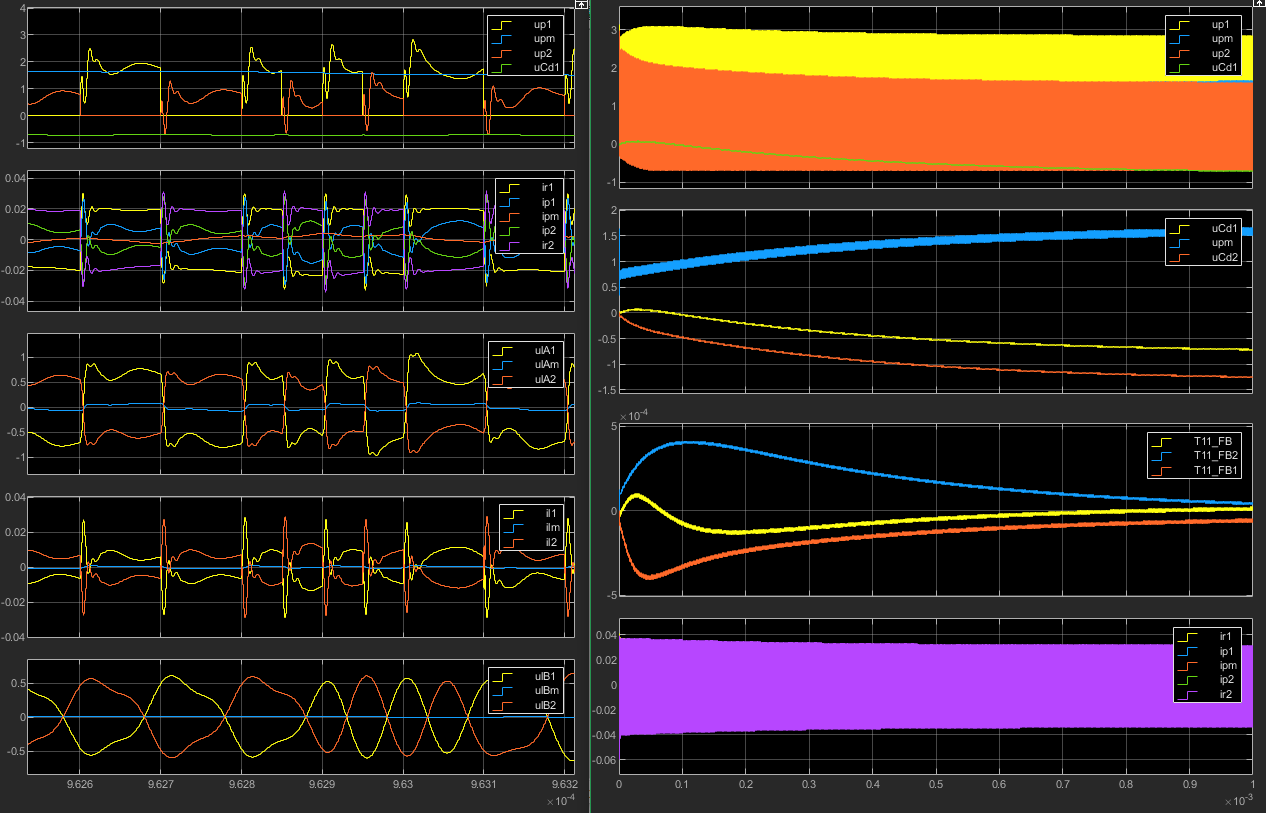

Differenz 2 mA in Stromquellen, ohne Korrektur, Mittelanzapfung 4.7 nF, mit CommonModeChoke

In der Simulation sind die Stromquellen auf 20 mA und 22 mA gesetzt. Dies kann zustande kommen wenn Toleranzen auftreten. Diese sind erwartbar zwar kleiner, aber der Effekt stellt sich ein.

Das Bild zeigt die Verhältnisse, wenn R7 und R8 (1 kOhm) zur Angleichung der Stromquellen nicht vorhanden sind. Die Stromdifferenz zeigt sich im Scope rechts 3. Track. Anfangs zeigt sich ca. 0.7 mA wirksame Stromdifferenz. Diese führt zum unterschiedlichen Aufladen von C4 und C5 auf einen Endwert (rechts, Track2) von ca, 1.5 V und 0.5 V. Der Endwert stellt sich nur dadurch ein, weil der defakto getriebene Strom reduziert wird aufgrund Begrenzung der Spannung an der Stromquelle auf die untere Gateschutzdiode im Open-Drain-Gatter. Dies ist sichtbar im linken Bild Track1, rot. Die Spannung an diesem Stromausgang ist meist nahe 0. Der Strom fließt dennoch, getrieben von der Einspeisung am anderen Wicklungsende (links, Track1, gelb, up1).

Für die Übertragund insgesamt hat das offensichtlich kaum einen Effekt, die Spannungen am anderen Ende der Leitung am 100 Ohm Terminator sehen gut aus. Aber die Stromquelle gerät in Begrenzungssituationen. Links: Deutlich sichtbar, Differenz in Spannungen an Stromquellen.

ohne C in Mittelanzapfung

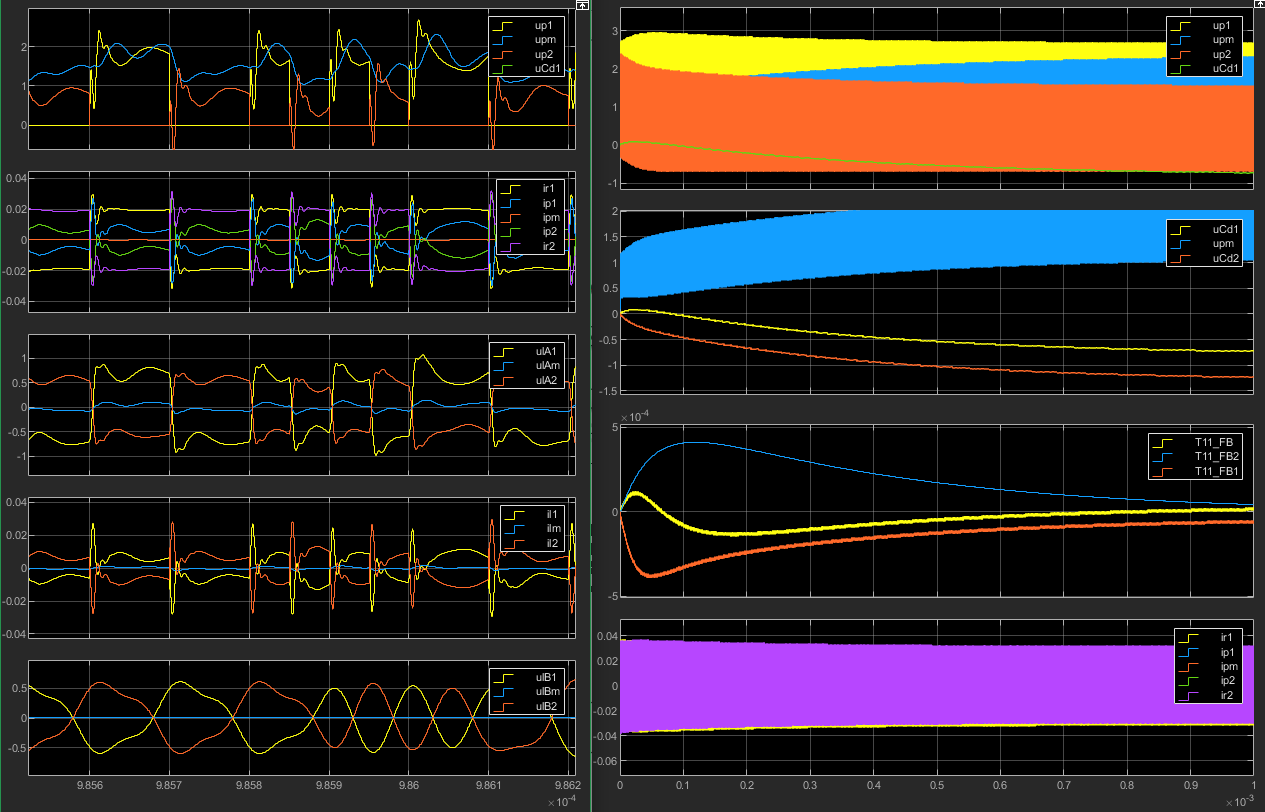

Differenz 2 mA in Stromquellen, mit Korrektur, Mittelanzapfung 4.7 nF, mit CommonModeChoke

Im folgenden Bild sind die Widerstände R7 und R8 mit je 1 kOhm in die Simulation einbezogen. Die Widerstände bewirken, dass die Stromquelle nicht unendlich hochohmig ist sondern mit 1 V/mA von der Ausgangsspannung abhängt.

Damit sind mit der Differenz der Spannungen an der Stromquelle nach Einschwingen der C4 und C5, Bild links Track1, aufgrund der unterschiedlichen Spannungen an den Stromquellen die Ströme gleich. Der Fehler wird ausgeglichen. Die C4 und C5 laden sich unterschiedlich auf bis zum Erreichen des stabilen Zustandes.

Deutlich im Bild sichtbar, mit gleicher Skalierung wie im Bild darüber: Die Stromausgänge gehen nicht in die Begrenzung. Links Track 1 rot up2 erreicht zwar im Überschwinger die -0.7 V der Gateschutzdiode grenzlastig, jedoch nicht wirklich in Begrenzung. Das vermeidet den Einfluss der begrenzenden Diodenspannung auf das Schwingungsverhalten am Kabel. Das ist zwar in dieser Simulation defakto nicht sichtbar, aber schon erwartbar. Gut sichtbar ist im Bild rechts, Track1, dass die Ausgangsspannung der Stromquellen weniger in die Begrenzung gerät.

ohne C in Mittelanzapfung, mit CommonModeChoke

3. Masse, Schirmung, Potentialtrennung, Stromversorgung (PoDL)

3.1. Schirmungstopologie SPE Kabel

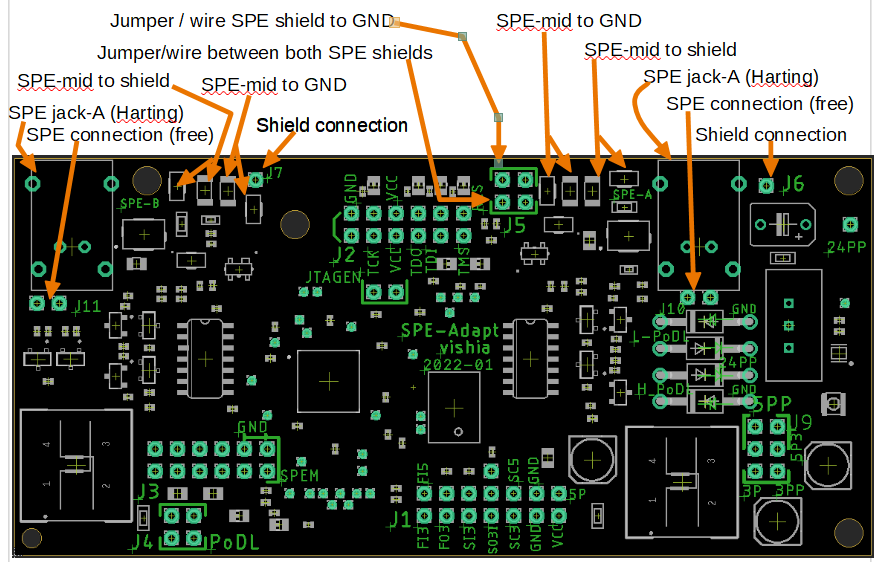

Die Schirmungen der beiden SPE-Plugs sind nicht miteinander verbunden, sind aber mit einem gelötetem Draht verbindbar (2 Lötaugen 0.8 mm/1.6 mm passend im Buchsen/Frontbereich).

Begründung: Eine Schirmung ist in der Regel nur einseitig auf Masse aufzulegen, damit Kreisströme vermieden werden über eine weitere bestehende Masseverbindung. Es hängt von der Anwendung ab:

Das Board ist hier im Topview aber mit der Rückseite in blau abgebildet, damit die Shield Verbindungen nachvollziehbar sind.

Wenn die Anwendung eine eigene feste Masseanbindung hat, die letztlich irgendwo anders mit der Schaltungsmasse verbunden ist, dann ist die Schirmung nicht auch mit der Schaltungsmasse zu verbinden wenn die Schirmung auf der anderen Kabelseite auf Masse liegt.

Bei einer Ringtopologie kann diese Massefrage für einzelne Geräte unterschiedlich sein. Daher ist eine feste Durchschleifung des Schirms vom einen auf das andere Kabel eben auch nicht zu empfehlen, wenn alle Partner über eigene Masseverbindungen verfügen. Es muss dann geklärt werden, wo der Kabelschirm jeweils geerdet ist.

Daher ist die Masseverbindung des Schirms individuell bestimmbar für beide Kabel.

In gleichem Zusammenhang ist eine Drahtbrücke im Abstand 2.54 mm (Jumper möglich) zu realisieren, um für beide SPE-Plugs den Schirm auf dieser Karte mit Schaltungsmasse zu verbinden. Ob die Verbindung realisiert wird, ist also ebenfalls von der Anwendung bestimmbar.

Beispiel für eine durchgeschleifte Schirmverbindung mit Schaltungsmasse-Anschluss:

Hat man eine kleine Anschaltung, einen Controller, der aus der PoDL versorgt wird und das Gerät hat selbst keine eigene Erdung, dann ist es sinnvoll sowohl die Schirme der SPE-Plugs zu verbinden als auch die Schaltungsmasse auf den Schirm zu legen. Das Gerät ist dann nur über diesen Schirm geerdet, nicht durch Gehäusebefestigungen etc. Das Gehäuse kann entweder schutzisoliert sein oder unabhängig und getrennt von Schaltung und Schirm auf eine Gehäuseerdung gelegt sein. EMV Einflüsse von diesem Gehäuse auf die Schaltung sind zu beachten. Ein Beispiel dafür ist eine Messeinrichtung für potentialgetrennte Signale beispielsweise nach einem Trenntrafo (Wechselstrommessung) oder als Anschaltung eine halleffektgekopplten Stromwandlers (z.B. von LEM). Hierbei ist das Signal selbst potenzialgetrennt ohne jeden Massebezug.

Frage auf welche Masse der Mittelpunkt der primären Wicklung des Ethernettrenntrafos (Würth) zu legen ist:

Es ist folgerichtig, dass dies nicht die Schaltungsmasse ist, sondern die Schirmmasse. Damit werden ggf. in die Kabeladern eingestreute Spikes symmetrisch auf den Schirm abgeleitet, der Trenntrafo hat damit zwischen Primär- und Sekundärwicklung möglicherweise nicht gefilterte Spikes, die aber zwischen der Schirmmasse und der Schaltungsmasse bestehen, nicht im Kabel. Wenn Schirmmasse des SPE und Schaltungsmasse letztlich an anderer Stelle (Gehäuse, Erde) niederohmig verbunden sind, dann sind diese Spikes eigentlich nicht da bzw. ebenfalls sowohl leitungsgebunden (äußere Masseverbindung mit möglicher Induktivität) bzw. kapazitiv (Gehäuse mit Erde) gefiltert.

Es ist ebenfalls im Einzelfall zu entscheiden, ob der primäre Mittelpunkt des Trenntrafo nicht doch auf die Schaltungsmasse gelegt werden soll. Dazu ist eine Bestückungsvariante vorgesehen, jeweils vom Mittelpung R-C auf Schirm und R-C auf Schaltungsmasse. Man kann diese Bestückung trotz SMD auch selbst ausführen oder ändern, da der Widerstand in der Bauform 1206 ausgeführt ist, nicht zu klein, also manuell lötbar.

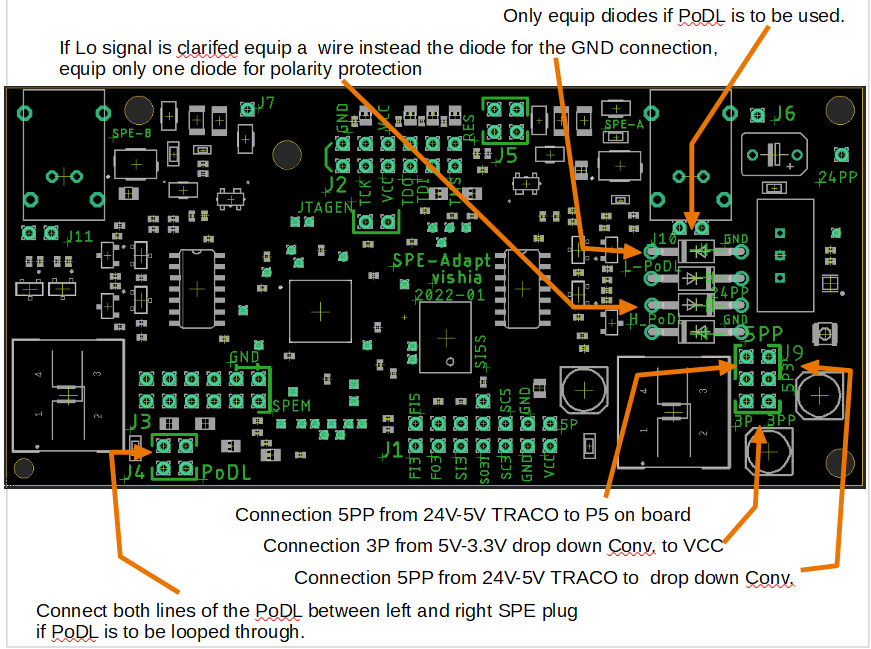

3.2. Power over Dataline, interne Stromversorgungsaufbereitung

Für die PoDL sind Entkopplungsdrosseln vorgesehen. Diese sollten für den flexiblen Einsatzfall nicht SMD-gelötet sondern bedrahtet sein. Damit kann für den Standardfall etwa 470 µA / 0.2..1 A vorgesehen werden. Wird mehr Strom übertragen, dann muss eine größere Drossel außen untergebracht werden. Es ist damit auch entscheidbar, ob mit Nichtbestückung der PoDL-Pfad im Ring unterbrochen wird (weil es mehrere Stromversorgungen gibt), also die eigene Karte nur einseitig versorgt wird.

Für dem einfachen Einsatzfall des Versuchsaufbaus ohne gemeinsamen Masseanschluss mehrerer Baugruppen oder für den Serieneinsatzfall eines potenzialgetrennten Sensors oder Aktors ist die preiswerte nicht potentialgetrennte Aufbereitung von 5 V aus 24 V vorgesehen. Dafür ist ein TRACO-Tiefsetzsteller von TRACO POWER TSR-1 Serie 1 A vorgesehen. Mit einer Baugröße von 12x8x10 mm integriert dieser sich gut in die Versuchsleiterplatte. Auch hier ist die Bestückung bedrahtet, kann und soll also manuell eingesetzt werden je nach Notwendigkeit. Die Eingansspannung kann hier 9 bis 36 V betragen, also sehr tolerabel. Die Ausgangsspannung ist 5V bei max. 1 A.

3.3. Potenzialgebundene Spannungsaufbereitung und potenzialgetrennter Aufbau

Die potenzialgebundene Spannungsaufbereitung darf nur verwendet werden wenn der Aufbau selbst, die Schaltungsmasse potenzialgetrennt ist. Ansonsten würden sich Kreissttröme über das SPE-Datenkabel bilden. Diese sind zwar für einen bestimmten Aufbau (im selben Schaltschrank…) möglicherweise nicht zu erwarten. Diese Aussage darf nicht gelten gelassen werden, denn bei Umbauten achtet man dann nicht mehr auf Details. Es gilt das Prinzip: Die Schaltungsmasse darf nicht anderweitig noch potenzialgebunden sein.

Allerdings ist eine kapazitive Anbindung der Schaltungsmasse an das Gehäuse (Erde) dringend zu empfehlen, beispielsweise über 100 Ohm + 1 nF. Ansonsten könnte es zwischen dem Gerätegehäuse oder Anschlussleitungsumgebungen und der Schaltungsmasse und anderen Schaltungsteilen undefinierte Felder geben, beispielsweise durch nahe WLAN-Sender oder störstrahlende Schaltnetzteile. 1 nF hat eine Impedanz von 1.6 kOhm bei 100 kHz. Das bedeutet dass durch EMV-Einfluss aufgefangene Ströme im Bereich 1 mA von Schaltnetzteilen ca. 1 V feldstärkebildend zwischen Gehäuse und Schaltungsmasse bilden. Diese Störspannung am Gehäuse hat dann weniger Einfluss auf Schaltungsteile (interne Signale) gegenüber einem Gehäuse ohne kapazitiven Bezug zur Schaltung, dass sich beliebig aufladen kann und feldstärkeerzeugend ist. WLAN-Frequenzen werden damit fast vollständig unterdrückt, es ist hier eher auf die induktive Anbindung der Kapazität zu achten.

Beispiele für potenzialgetrennte Schaltungen sind:

-

Versuchsaufbau-Platine mit Controller, der Anschluss an ein Notebook wird entweder über einen USB-Potenzialtrenner durchgeführt, oder der Notebook wird auf die Schaltungsmasse bezogen und ist selbst potenzialgetrennt (im Konkretfall in Eigenverantwortung zu entscheiden). Adäquates gilt für den Anschluss einens Scopes für Messungen.

-

Controller, der beispielsweise potenzialgetrennte Analogwerte aufbereitet, wie sie von magnetisch getrennten Wandlern geliefert werden (LEM mit Hall-Effekt-Messung oder magnetische Stromwandler). Hier ist der Wandler selbst potenzialgetrennt aber ggf. in einer gestörten Umgebung.

Für komplexere Einheiten, die einen eigenen Schaltungsmassebezug benötigen, ist dieser einfache potenzialgebundene TRACO-Wandler nicht einsetzbar. Es ist außen eine entsprechende potenzialgetrennte DC/DC-Wandlung anzuschließen (wie bei SPE PoDL empfohlen).

3.4. interne Umsetzung 5 V auf 3.3 V

Das SPE-Kärtchen benötigt intern 5 V für die Treiber der Ströme und 3.3 V für die FPGA-Schaltung. Je nach Verhältnissen an ein angeschlossenes Controllerkärtchen könnten diese beiden Spannungen vom Controllerkärtchen mit eigener Stromversorgung geliefert werden, also weder über PoDL noch über eine eigene 5V/3.3V-Umsetzung. Das hat den Vorteil dass die gemeinsamen Schaltungspegel zueinander passen.

Unter Nutzung des PoDL kann es anders herum gewählt werden: Das SPE-Kärtchen versorgt den Controller mit max. 0.95 A für 5 V und bis zu 1 A für 3.3 V. Für viele Anwendungen ist das ausreichend.

Über Drahtbrücken oder Jumper ist einstellbar, ob die interne 3.3 V genutzt wird oder am Jumperpin oder Lötauge von außen zugeführt wird. Gleiches gilt für die 5 V.

Auf dem Board, Top view sind rechts drei Jumper.

Über der PoDL-Drossel sind Dioden untergebracht, die wahlweise bestückt werden können.

In diesem Bild ist der TRACO-Konverter von 24 V auf 5 V nur durch drei Lötaugen präsentiert, Bestückung anwenderdefiniert.

4. FPGA Anschlüsse

4.1. FPGA Programmierung, JTAG und Reset

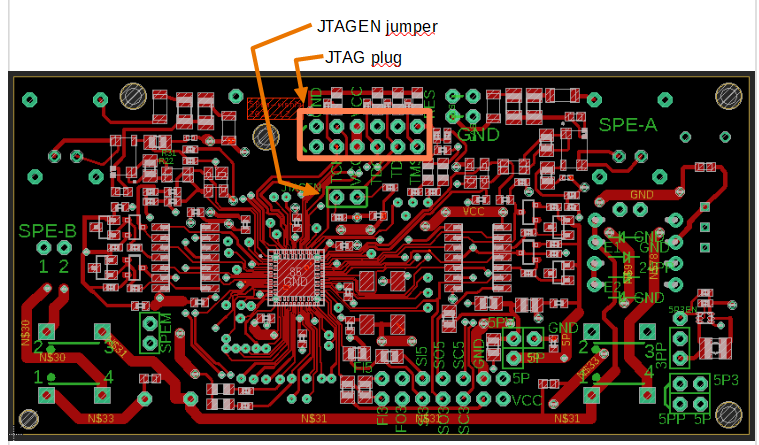

Das FPGA wird über JTAG Signale programmiert.

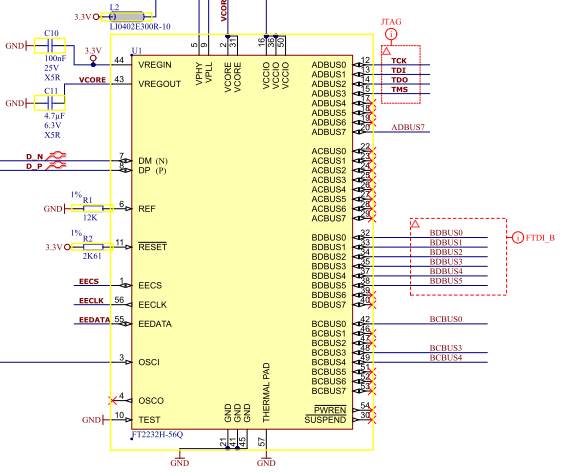

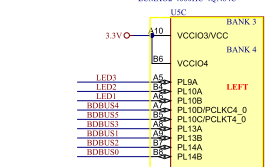

Bei einem Musterkärtchen von Trenz Elektronik

ist ein sogenannter FTDI-Chip on board. Dieser sorgt für die Umsetzung USB-Anschluss (vom PC) auf die JTAG-Signale zum programmieren. Die Schaltung dieser Karte bezüglich FTDI und JTAG sieht wie folgt aus (Kopie Trenz Elektronik Dokumente):

Die Bilder zeigen nur die relevante Auszüge aus den Schaltplänen, über den obigen link auch abrufbar.

Links ist der FTDI-Schaltkreis. Dies ist ein relativ universeller Umsetzer von USB auf beliebige Ausgangssignale, der allerdings oft für JTAG genutzt wird (auch bei Controller-USB-Interfaces):

Die JTAG-Funktion bestimmt der USB-Treiber im PC. Für das konkrete Evaluationsboard für den gleichen FPGA wurden noch mehr Signale angeschlossen, die nicht für das Programmieren sondern für den PC-Zugriff auf den FPGA (Debug etc.) interessant sein können. Für das FPGA-Evaluationsboard wurden die rechts sichtbaren FPGA-Pins dort angeschlossen, die ansonsten nicht weiter auf Lötaugen gelegt worden sind.

Dieses USB-Interface ist nicht Bestandteil des vorliegenden SPE-Evaluationsboards. Kurze Begründung: Das FPGA sollte für die Standardanwendung fest programmiert sein (anders als beim FPGA-Evaluationsboard). Für das Progammieren des FPGA kann ein entsprechendes Adapterkärtchen verwendet werden. Für JTAG gibt es mehrere Hardwareangebote, so auch von Trenz selbst:

Eine andere Möglichkeit ist: link: https://www.mouser.de/ProductDetail/ftdi/ft2232h-mini-module. Dies ist eine direkte universelle Umsetzung des FTDI-Schaltkreises auf ein Board.

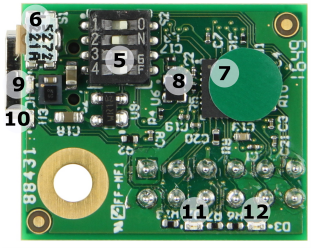

Speziell für die Lattice-Programmierung wurde ein weiterer Adapter gefunden:

Man kann solche Adapter mit den JTAG-Pins verbinden, bei Bedarf damit den FPGA programmieren bzw. nach dem Test der SPE-Karte die Standardprogrammierung aufbringen.

Die Steckkontakte wurden so gewählt, dass der Trenz-Programmieradapter direkt darauf passt. Andere Programmieradapter sind mit Kabeln passend verbindbar.

Die Trenz-Karte wird oben aufgesteckt, ragt etwas über und geht nach links weg über einen der SPE-Adapter mit dem USB-Kablel. (SPE-Adapter nach oben). Das folgende Bild zeigt links die sich ergebende Ansicht der aufgesteckten Karte, dabeben diese Trenz-Adapterkarte umgeklappt, so dass der Steckverbinder sichtbar ist:

Diese Karte sollte mit Verlängerungs-Stecker aufgesteckt werden da sonst der USB-Anschluss mit dem SPE-Plug ins Gedränge kommt, oder es sollten lange Lötstifte verwendet werden. Jedenfalls sollte das Programmieren auch bei SPE-Anschluss betrieben werden können. Das ist nur für den Fall, dass am FPGA (noch) entwickelt werden muss.

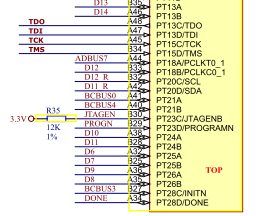

Für den Trenz-Programmieradapter gibt es Variationen, abhängig von einer Firmware auf einem speziellen CPLD. Für den Standard gibt es folgende Belegung:

Pins in Reihenfolge wie von oben auf SPE-Board:

1 GND RxD VCC TxD Led Reset GND TCK VIO TDO TDI TMS

-

Die untere Reihe repräsentiert die JTAG Signale. Diese sind mit den entsprechenden Pins im FPGA verbunden:

-

TCK = A45

-

TDO = A48

-

TDI = A47

-

TCK = A45

-

TMS = B34

-

-

Reset = B29 in der oberen Reihe ist mit dem Reset bzw. PROGRAMN vom FPGA verbunden = B29. Das Pin ist direkt mit C31 = 100 nF auf GND bezogen und wird mit R38 = 10 k auf High gezogen. Mit der sich ergebenden Zeitkonstante von 1 ms wird das FPGA nach Erreichen der VCC_Power noch im Reset gehalten. Das hilft, wenn die VCC etwas unsauber im Bereich < 1 ms kommt. Das Reset-Pin entläd den C31 mit 470 Ohm und führt damit auch im Betrieb einen erneuten Reset aus, wenn das Pin in der FPGA-Programmierung nicht anderweitig belegt worden ist.

-

Die Pins für RxD, TxD und Led vom Trenz-Adapter sind mit Pins im FPGA verbunden, die user-spezifisch ausführbar sind. Dies sind keine Standard-Funktionen im FPGA. Auch andere FTDI-Adapter verfügen über RxD und TxD, die softwareseitig im PC über USB versorgt werden kann, Treiber für COM-Schnittstellen. Bei Controllern werden diese meist mit der Standard-UART-Schnittstelle verbunden.

-

RxD = B32 (RXDT)

-

TxD = A42 (TXDT)

Die Led ist auf dem Tren-Kärtchen eine optionale Anzeige:

-

Led = A41 (LEDT)

Wichtig: Die JTAG-Pins sind als solche aktiv wenn das Signal JTAGENB = B30 aktiv high erkannt wurde bei Power on bzw. wenn das Pin B30 nicht anderweitig umprogrammiert wurde. Dazu ist ein Jumper auf JTAGEN zu stecken bzw. diese Lötaugen zu verbinden (damit JTAG immer aktiv). Über R35 = 470 Ohm wird dieses Pin auf 3.3 V gezogen. Ist der Jumper nicht gesteckt, dann ist JTAGENB = B30 über R36 = 10 kOhm auf 0 terminiert. Das Pin kann als Anwenderpin verwendet werden, Beispiel für ein Testsignal, das dann statt dem Jumper abgegriffen wird. Die Last von 10 kOhm sollte kein Problem darstellen.

Für das Standard-FPGA-Design im Betrieb werden diese Stecker als Testsignale genutzt. (Scope-Anschluss binäre Signale). Es ist beim Design des FPGA zu beachten: Nach Programmierung gilt die Belegung laut FPGA-Schaltplan. Wird PROGRAMN = B29 nicht anderweitig belegt, nur dann gilt es als Reset. Ein Reset wird aber immer durch Power-off/on erzeugt.

4.2. SPI- und Framesignal Anschlüsse am FPGA

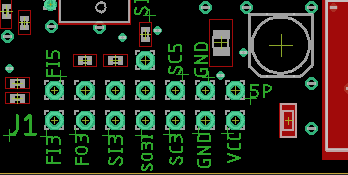

Entsprechend dem FPGA-Design ist die SPI-Schnittstelle an folgenden Pins auf 1.6 mm / 0.8 mm Lötaugen entweder für direkte Bedrahtung oder auf einen Stift herausgeführt:

-

FI3 = A25: FrameIn Signal, löst das SPI-Interface aus entweder für Datensenden oder zum Vorbereiten des Datenempfanges.

-

FO3 = A8: FrameOut Signal, kommt wenn das StartFrameDelimiter nach Synchronisation empfangen worden ist. Mit diesem Signal ist eine Zeit im Zyklus zu nehmen (Capture-Funktion einer PWM), die der Zeitzyklussynchronisation dient.

-

SC3 = A30: SPI_CLK: Dieses Signal wird vom FPGA erzeugt, Clock für SPI. Das FPGA ist der SPI-Master. Die ersten 32 SPI_CLK Signale kommen nach FRAME_IN

-

SI3 = A26: SPI_MISO: Input des SPI-Datensignals vom Controller (Output, Slave) zum FPGA.

-

SO3 = A28: SPI_MOSI: Output des SPI-Datensignals vom FPGA (Master) zum Controller (Slave).

Diese Signale arbeiten mit dem 3.3 V Pegel am FPGA. Hat der Controller nur 5 V In/Outputs, dann sind diese Signale als entsprechende 5 V Signale abgreifbar bzw. zuführbar, Nutzung der Pins darüber.

Am Stecker ist ebenfalls GND, VCC (3.3 V) und 5P (5 V) vorhanden. Damit kann das Controllerboard entweder versorgt werden oder anders herum, siehe Kapitel Power over Dataline, interne Stromversorgungsaufbereitung.

Für die Outputs FO5, SC5, SO5 werden negierte Open-Drain-Gatter der IC1 und IC3 verwendet. Diese sind mit 470 Ohm ausgeführt. Damit ergibt sich bei Cp=20 pF (erwartbar, kurze Verkabelung) eine Zeitverzögerung von 20 ns gerechnet für 85% Pegelerreichung. (Ts=10 ns). Ist die kapazitive Last größer, dann könnten diese R17, R13 und R14 auch gegen bis zu 270 Ohm ausgetauscht werden. Für diesen Zweck wurde die Bauform 0805 gewählt, die generell mit einer Lötnadel noch beherrschbar ist.

Der zusätzliche Strombedarf beträgt bis zu 30 mA bzw. 60 mA bei 270 Ohm. Um dies zu verhindern, wenn die 5 V Ausgangssignale überhaupt nicht benötigt werden, sind die pullup über einen Jumper oder Drahtbrücke zwischen 5PV und 5P (Beschriftung) zu aktivieren. Alternativ ist 5PV auf GND zu legen, der Jumper passt nur auf eine der beiden Möglichkeiten. Offenlassen geht prinzipiell auch. Ist die 5PV nicht oder mit GND verbunden, dann wird der Strom in die Open-Drain Ausgänge verhindert. Die Signale sind dann immer 0 (bei GND-Anschluss).

4.3. Weitere Testpins am FPGA

Vom FPGA sind alle Pins herausgeführt, allerdings teils auf 1 mm Lötaugen, die nur mit einer feinen Lötnadel anwenderseitig mit einem Cu-Volldraht max. 0.3 mm belegbar sind. Das kann benutzt werden für spezifische Erweiterungen, die individuell als Test ausgeführt werden. Die 1 mm-Lötaugen können auch mit einer spitzen und konischen Nadel als Testpin abgegriffen werden. Ist die Nadel passend konisch, dann hält dies in einem vorsichtigen Versuchsaufbau.

4.4. SPE Input und Output

Die Differenzeingangssignale sind nach dem Trenntrafo T1 und T2 getrennt mit der CommonModeChoke L1 und L2 und begrenzt mit der TVS Diode DFN1210, 3.3 V auf folgende FPGA-Pins gelegt:

-

RXD1H = A36

-

RXD1L = A35

-

RXD2H = A1

-

RXD2L = A2

Die Pins sind damit gegen Überspannungen geschützt. Die Pins sind im FPGA entsprechend zueinandergehörige Differenzeingänge mit "true LVDS" Kennzeichnung. Auf genau diese Pins wirken die Stromquellen der Ausgangstreiber. Die Spannung aus den Stromquellen ist ebenfalls auf 3.3 V begrenzt, womit die Eingänge prinzipiell geschützt sind. Die Stromquellen könnten ohne Begrenzung bis zu ca. 4.3 V bei 20 mA erzeugen. Die Eingänge sind zusätzlich im FPGA mit Gateschutzdioden zu programmieren. Die Leitungsführung ist insgesamt parallel und kurz geführt. Auf ein zusätzliches Wiring (wechseln der Seite) wurde verzichtet.

Die SPE-Outputs um die Stromquellen auf GND zu schalten sind:

-

TXD1HG = A33

-

TXD1LG = A38

-

TXD2HG = A6

-

TXD2LG = A3

Die Ausgänge sind negiert zu bilden, da durch IC1 und IC3 dann nochmals negiert (Open Drain Treiber). Die Pins liegen nicht auf zueinandergehörigen Differenzinput-Pärchen, das ist nicht notwendig. Die Verdrahtung richtet sich nach einem günstigen PCB-Layout.

Die Stromquellen der SPE-Outputs sind abschaltbar mit folgenden Signalen:

-

TXD1HP = A32

-

TXD1LP = A34

-

TXD2HP = A5

-

TXD2LP = A7

Low bedeutet: Stromquelle aktiv. Die Stromquellen sind für diejenige Richtung abzuschalten, die auf Empfangsrichtung geschaltet ist (diese Pins High). Dazu sind auch die Pins TXD**G alle auf Low zu schalten. Damit sind die Sendeausgänge durchweg hochohmig.

Diese Pins sind auch schaltbar während der Sendeübertragung immer entgegensinning TXD*G mit TXD*P. Damit wird ein Stromtreiben vermieden, wenn der Stromausgang auf GND über OpenDrain gezogen ist. Es wird damit Strom gespart. Allerdings ist das Timing abzustimmen: Die Stromquellen müssen etwas eher wieder zugeschaltet werden, bevor das OpenDrain inaktiv schaltet, da die Stromquellen etwas langsamer sind (ca. 10..20 ns). Das kann im FPGA programmiert werden.

4.5. Mastersignal für SPE

Mit einem Jumper oder Drahtbrücke an SPEM wird das Pin

-

SPEM = A9

auf GND gezogen. Es ist im Standard-FPGA-Design als Input mit pullup versehen und schaltet bei Low-Input die SPE-Master-Funktion zwangsweise ein. Das bedeutet, dass ohne Programmierung das FPGA keine Empfangsdaten weitergibt. Läuft ein Ring nur mit SPE-Slaves ohne Softwareprogrammierung hoch, dann kann sich ein Eigenleben ausbilden wenn es eine Anregung gibt. Das wird durch das Master-Pin verhindert. Ein Master kann parallel dazu ohne diesen Jumper auch softwareseitig bestimmt werden. Das kann wichtig sein für eineen Connectiontest im Ring.