Last page backward

# UFBgI – Unified Function Block graphic language

# Diagrams for UML and Function Blocks drawn with OpenOffice or LibreOffice

Dr. Hartmut Schorrig www.vishia.org

2024-04-15

# **Table of Contents**

| 1 | Open/Libre Office for Graphical programming                                                                       | 8    |

|---|-------------------------------------------------------------------------------------------------------------------|------|

| 2 | Join FBlock Diagrams and UML-Class Diagrams                                                                       | 9    |

| 3 | Approaches for the graphic, basic considerations                                                                  |      |

|   | 3.1 Question of sizes and grid snapping in diagrams                                                               | . 10 |

|   | 3.2 Using figures with style sheets for elements                                                                  |      |

|   | 3.3 Connectors of LibreOffice for References between classes                                                      | .15  |

|   | 3.4 Connect Points for more complex references                                                                    | .16  |

|   | 3.5 Diagrams with cross reference Xret                                                                            | . 17 |

| 4 | Working flow creating your own diagrams                                                                           | .18  |

| 5 | Overview capabilities and concepts of the UFBgl                                                                   | . 20 |

|   | 5.1 All Kind of Elements with there Style Sheets                                                                  | . 20 |

|   | 5.2 FBlock or class, name and type                                                                                | . 22 |

|   | 5.3 Show same FBlocks multiple times in different perspectives                                                    | .22  |

|   | 5.4 Function Block and class diagram thinking in one diagram and the ObjectOrientation and also Functional aspect | .23  |

|   | 5.5 More as one page for the FBlock or class diagram                                                              |      |

|   | 5.6 Using events instead sample times in FBlock diagrams                                                          | .26  |

|   | 5.7 Storing the textual representation of UFBgl in IEC61499                                                       | .28  |

|   | 5.8 Source code generation from the graphic                                                                       | . 29 |

|   | 5.9 Run and Test and Versioning                                                                                   | . 30 |

| 6 | . Details                                                                                                         | . 32 |

|   | 6.1 Data types                                                                                                    | . 32 |

|   | 6.1.1 One letter for the base type:                                                                               | . 32 |

|   | 6.1.2 Unspecified types:                                                                                          | . 33 |

|   | 6.1.3 Array data type specification                                                                               | . 34 |

|   | 6.1.4 Container type specification                                                                                | . 34 |

|   | 6.1.5 Structured type on data flow                                                                                | . 35 |

|   | 6.1.6 Data type forward and backward propagation                                                                  | .36  |

| 6 | .2 One Module, Inputs and Outputs, page layout                                                                    | . 38 |

|   | 6.2.1 Module in file organized in pages                                                                           | . 38 |

|   | 6.2.2 Module pins                                                                                                 | . 38 |

|   |                                                                                                                   |      |

|   | 6.2.3 Order of pins                                                            | . 40 |

|---|--------------------------------------------------------------------------------|------|

|   | 6.2 Expressions inside the data flow                                           | . 42 |

|   | 6.2.1 Expression parts as input                                                | . 42 |

|   | 6.2.2 More possibilities of DinExpr                                            | . 43 |

|   | 6.2.2.1 Variables in the DinExpr                                               | . 44 |

|   | 6.2.2.3 Syntax/semantic of DinExpr                                             | . 44 |

|   | 6.2.2.3 Some examples for DinExpr                                              | . 46 |

|   | 6.2.3 Any expression in FBexpr                                                 | . 46 |

|   | 6.2 4 Output possibilities                                                     | . 46 |

|   | 6.2.5 Set components to a variable                                             | 47   |

|   | 6.2.6 Output with ofpExprOut                                                   | 47   |

|   | 6.2.7 FBexpr as data access                                                    | . 48 |

|   | 6.2.8 Type specification in expressions                                        | . 48 |

|   | 6.2.9 FBoper, operation for a FBlock                                           | . 49 |

|   | 6.2.10 FBexpr capabilities compared to other FBlock graphic tools              | 49   |

|   | 6.3 Possibilities of FBlocks                                                   | . 50 |

|   | 6.3.1 Difference between class, type and instance                              | . 50 |

|   | 6.3.2 FBlocks for each one function, data – event association                  | 51   |

|   | 6.3.3 Aggregations are corresponding to ctor or init events                    | . 52 |

|   | 6.3.4 FBlocks for operation access in line in an expression                    | . 53 |

|   | 6.4 Drawing and Source code generation rules                                   | . 55 |

|   | 6.4.1 Writing rules in the target language used from generated code from UF    | _    |

|   | 6.4.2 Life cycle of programs in embedded control: ctor, init, step and update. | 56   |

|   | 6.4.3 Using events in the module pins and FBlocks, meaning in C/++             | 57   |

|   | 6.4.4 More possibilities, definition of special events                         | . 59 |

|   | 6.5 Converting the graphic – source code generation                            | . 60 |

|   | 6.5.1 calling conversion with code generation                                  | . 60 |

|   | 6.5.2 Templates for code generation                                            | . 62 |

| 7 | 7 Discussion about graphic presentation approaches and implementations         | 64   |

|   | 7.1. Data and event flow                                                       | . 64 |

|   | 7.2. FBtype kinds and their usage (due to IEC61499)                            |      |

|   | 7.3. Construction, init, run with several step times or events and shutdown    |      |

|   | 7.4. Prepare and update actions                                                |      |

|   | · · ·                                                                          | . 69 |

|   |                                                                                |      |

| 7.4.1. Example prepare and update for boolean logic                              | . 69 |

|----------------------------------------------------------------------------------|------|

| 7.4.2. State of the art, ignoring prepare and update concept                     | .70  |

| 7.4.3. Example prepare and update in source text languages (C/++)                | .70  |

| 7.4.4. Example prepare and update in 4diac with MOVE-FBlock                      | .72  |

| 7.4.5. Example prepare and update in Simulink                                    | .77  |

| 7.4.6. Example prepare and update for odg Graphic code generation (Libre Office) | . 79 |

| 7.5. How to associate the prepare to the update event                            | .81  |

| 8 Inner Functionality of the Converter Software                                  | . 83 |

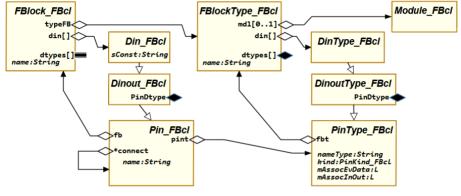

| 8.1 Data Model data classes                                                      | . 84 |

| 8.1.1 FBtype_FBcl                                                                | . 84 |

| 8.1.2 FBlock_FBcl                                                                | . 85 |

| 8.1.3 Pin_FBcl and PinType_FBcl                                                  | . 85 |

| 8.1.4 PinType_FBcl                                                               | . 86 |

| Operations or Actions assigned to the Pins, code generation                      | .86  |

| Association between Event and Data Pins                                          | . 87 |

| Associaton between Input and Output pins                                         | . 87 |

| Association between prepare and update events                                    | .87  |

| Multiple pins                                                                    | . 87 |

| Data Types                                                                       | . 88 |

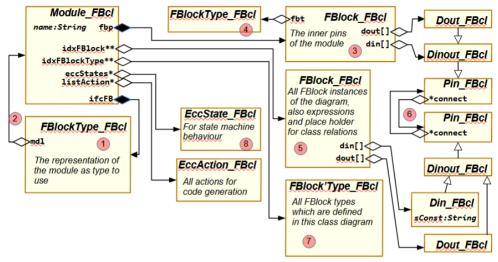

| 8.2 Module with FBlocks                                                          | . 90 |

| 8.3 Write instances for FBlock_FBcl, FBtype_Fbcl, Module_FBcl                    | .91  |

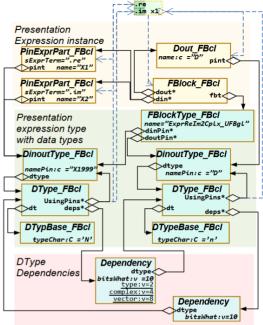

| 8.4 DType_FBcl and DTypeBase_FBcl                                                | . 92 |

| 8.4.1 Using DType_FBcl                                                           | . 92 |

| 8.4.2 Using DTypeBase_FBcl                                                       | . 93 |

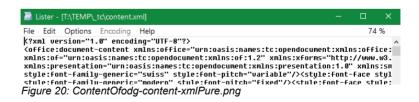

| 8.5 Read data from LibreOffice odg files                                         | . 94 |

| 8.5.1 The file format of odg – content.xml                                       | . 94 |

| 8.5.2 Read content.xml to internal data                                          | . 95 |

| 8.5.3 Sorting data from XML mapping to UFBgI data                                | .97  |

| 8.5.5 Preparation of Expressions from odg                                        | . 97 |

| 8.6 Read data from Simulink                                                      | . 98 |

| 8.7 Read data from IEC61499 text files (fbd)                                     | . 98 |

| 8.8 Forward and backward declaration of data types                               | 100  |

| 8.8.1 Forward/backward propagation of dedicated pins                             | 100  |

| 8.8.2 Forward and backward propagation of non dedicated pins                     | 100  |

| 8   | 3.8.3 Forward declaration for depending pins of a FBtype                  | .100  |

|-----|---------------------------------------------------------------------------|-------|

| 8.9 | <i>9 Identification of the event flow due to data flow</i>                | .104  |

|     | 3.9.1 UFBgl: Binding event to data on in/outputs                          |       |

| ε   | 3.9.2 Resulting evout because of evin of a FBlock                         | .104  |

| ε   | 3.9.3 Some Contemplation to bind data to events, event cluster            | . 105 |

| 8   | 3.9.4 Temporary info in pins for data→event processing                    | .106  |

| 8   | 3.9.5 UFBgl: Build the event chain                                        | . 107 |

|     | 8.9.5.1 Start on module's evin                                            |       |

|     | 8.9.5.2 propagate one step forward                                        | . 107 |

|     | 8.9.5.3 Check all other dinDst                                            | . 107 |

|     | 8.9.5.4 Discard the step if not all doutSrcOther are driven by events yet | .108  |

|     | 8.9.5.5 Connect the events if all doutSrcOther are driven by events       | .108  |

|     | 8.9.3.6 Put evoutDst in the queue to continue                             | 110   |

| 8.1 | 10 Code generation due the to event flow                                  | 113   |

| e   | 6.6.3 Using a templates for code generation with OutTextPreparer          | 113   |

| 8   | 3.10.5 Tracking the event chain for a module's operation                  | 115   |

| e   | 6.6.2 Access operation to dout, arguments                                 | 115   |

| 8   | 3.10.6 Code generation for one FBlock, one line or statement in the chain | 115   |

|     | 8.10.6.1 Generation with a FBlock specific script                         | 115   |

|     | 8.10.6.2 Expression to set an element in a variable                       |       |

|     | 8.10.6.x Set the module output                                            | . 116 |

|     | 8.10.6.x create code for ctor                                             | . 116 |

|     | 8.10.6.x create code for init                                             |       |

|     | 8.10.6.x call any FBlock content                                          | . 116 |

| ε   | 3.10.12 Code generation for Fbexpr                                        |       |

|     | 8.10.12.1 What does genExprTerm()                                         | . 118 |

# **Table of Figures**

| Figure 1: View 40%                          | 11 |

|---------------------------------------------|----|

| Figure 2: View 100%                         | 11 |

| Figure 3: Example for a Module Diagram      | 12 |

| Figure 4: OFB/DflowStructData1.png          | 35 |

| Figure 5: OFB/DflowStructData1.png          | 35 |

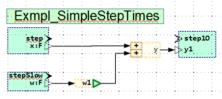

| Figure 6: Smlk / Exmpl_SimpleStepTimes.png  | 64 |

| Figure 7: 4diac / Exmpl_SimpleStepTimes.png | 64 |

### page 6

| Figure 8: odg / Exmpl_SimpleStepTimes.png             | 65  |

|-------------------------------------------------------|-----|

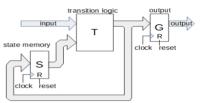

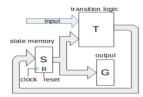

| Figure 9: Moore automat                               | 68  |

| Figure 10: Moore automat 2                            | 68  |

| Figure 11: data flow with qout                        | 68  |

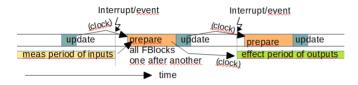

| Figure 12: Timing prepare, update and hardware access | 69  |

| Figure 13: Example binary logic prep & update         | 69  |

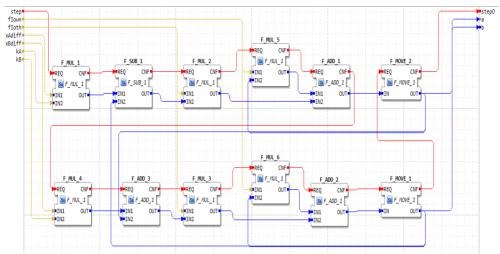

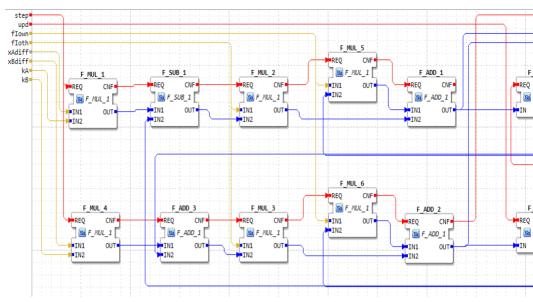

| Figure 14: Example 4diac prep & update                | 72  |

| Figure 15: Example 4diac prep & update                | 72  |

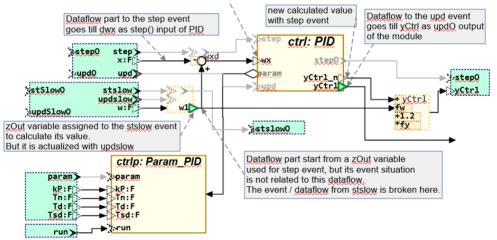

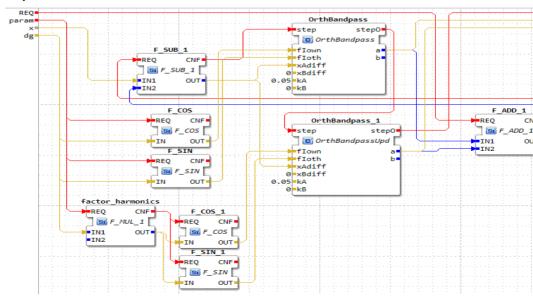

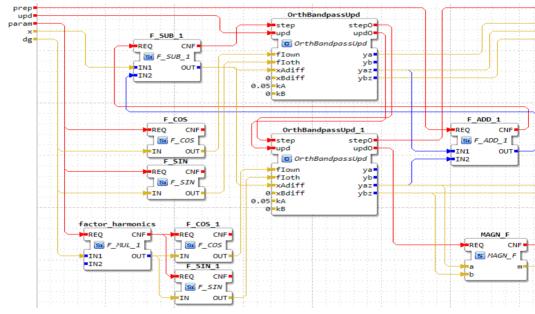

| Figure 16: OrthBandpass without update event          | 73  |

| Figure 17: FBlock_FBtype_Pin.png                      | 84  |

| Figure 18: Module_FBcl                                | 90  |

| Figure 19: ContentOfodg.zip.png                       | 94  |

| Figure 20: ContentOfodg-content-xmlPure.png           | 94  |

| Figure 21: ExprReIm2Cplx_DTypeDeps.png                | 101 |

| Figure 22: smlk/Testcg_MdlTstepSmlk.png               | 105 |

| Figure 23: smlk/ParallelSimple_smlk_EvChainBack.png   | 105 |

### page 7

## 1 Open/Libre Office for Graphical programming

One of the advantages of textual programming is: You can visit your program code with any desired editor, such as Notepad++, or VIM on Linux or just a powerful Integrated Development Environment. For development of course, compiler tool suites are necessary. But to discuss content, behavior, look whats happen you need only standard tools. For long time maintenance it means it may be sufficient only to have the source code itself. if maintenance actions can be done by parametrization (with given Operation and *Monitoring* tools), or for update the program vou need only the compilation tools or possible use newer versions of compilation tools which are compatible.

If you use graphical programming, then the graphical sources can be viewed often only with the original tools which may be vendor specific, need licenses to use etc. Sometimes older source files cannot be opened with newer (currently in use) versions of the tools. It means only for view what is contained in your device you need a specific tool. Additional often code changes are sophisticated in the tool chain, needs specific knowledge (about set options etc.).

This may be one reason that textual programming is preferred, though for the graphical programming it was rumored also for more as 20 years, it would be replace the textual programming because of some advantages.

That's why graphical programming is the playground for some big tool providers, whereas different approaches are given with the tools which are not compatible. Whereas textual programming is also familiar for common software, sometimes Open Source.

The second reason to favor textual programming is: The sources are immediately comparable with simple text diff

tools. And the third reason is: Tools are interchangeable, the source is always understandable as text source.

Now, to favor the graphical programming, this paper offers the idea and shows approaches related with usable software for content evaluation to use a common graphical draw tool for the graphical programming, which is usable for everybody without effort, which is compatible also with some other tools and which is enough powerful to use. For that *LibreOffice* and also *OpenOffice* was tested to draw the diagrams, and a translator to evaluate the content was written (just in progress). This concept is presented here.

Some basic ideas are:

- Use Style Sheets to designate semantic information to graphical blocks,

- Evaluate it reading information from the odg file, it is a simple zip file containing XML information

- Translate the content to other graphic formats for the specific tool or make the own code generation.

A second approach of this work is: For graphical programming the familiar idea to use Function Block Diagrams (FBD) to present functional content are combined with important features of the UML class diagrams. All in all the Function Blocks (FBlocks) are seen as instances of classes, which is self evident often for code implementation (in C++) but also in C where Object Oriented classes can be implement with struct data and the appropriate operations for this data. It means the FBlock Diagrams are advanced with UML features of class diagrams.

And also, UML class diagrams (without the FBlock idea) can be drawn and translated also with this approach.

## 2 Join FBlock Diagrams and UML-Class Diagrams

The **Unified Modeling Language** (UML) was created in the beginning of the 1990<sup>th</sup> based on different existing modeling approaches, firstly by Grady Booch, Ivar Jacobson and James Rumbaugh [1]. Another contribution to UML comes from David Harel [2] who had development state machine technology firstly introduced with his own tool "*Statemate*" and then applied to the UML tool *Rhapsody* (original from I-Logix, now IBM).

The focus of UML was also code generation for particular devices, but also the approach of commonly describing of systems which can be applied to particular software, with focus of Object Orientation.

In opposite, the technology for *Function Block Diagrams* (FBD) inclusively code generation for particular usual firstly automation devices was created already in the 1960<sup>th</sup> with the IEC 61131 Norm for "*Programmable Logic Controllers*". It was also similar used for some other approaches such as LabVIEW [3] or simulation tools. Especially Simulink from Mathworks [4] is used here for some comparisons with the here shown technology. This tools has its basics in the 1980<sup>th</sup> but currently further developed and used.

Both approaches, the UML and the FBD tools are designated as "*model driven development*". But there are not related. The FBD tools does not use diagrams from the UML, and it is usual not seen as "Object Oriented" and the UML seems not accept a diagram kind which is firstly for a particular software or device and not for a commonly described system.

Usual the code generation is familiar from the FBD tools. In UML code generation generates only the frames of the classes respectively instances, it is not so frequently used. The FBD tools focus only to the functional aspect of a device or a software. The operation system and managing to properly run the software (organization of threads, hardware access etc.) is usual done by specific settings (for example the "hardware config" part of configuration for automation devices with the Siemens TIA portal). The system itself is hard coded given and does not need an elaborately description presentation.

In opposite, the UML focuses to the whole system. For example the operation system itself is a "*component*", which is presented with interactions etc. in the component diagram. Also some hardware components.

In this manner the here presented combination of the UML Class and the FBlock diagram is only a part of a possible "UML 3.0". It does not replace all basics from UML, of course. It is only a contribution for this imagined UML 3.0.

How to name this combination of a FBlock and Class Diagram ... Let's use the abbreviation **UFB**. The "U" comes from the UML influence, also means "Unified". The diagram, graphical programming is named **UFBgI** with "gl" as "graphic language". A textual representation of the same content should be named **FBcL** as "Function Block connection Language". The focus to the UML is not presented in this abbreviation, but UML is familiar and recognizable.

What else: The **event connection** between FBlocks are also used here as important part. Events are familiar in UML for state machines. An Event connection is also used in FBlock Diagrams with the standard IEC61499 [5] for automation devices as a basically feature. Also in Simulink events are designated and used for "*triggered subsystems*" as well as for state machines. But events are familiar also in UML for *State Charts*, and should be familiar in Object Orientation.

## 3 Approaches for the graphic, basic considerations

This chapter shows how capabilities of **Open-** or **LibreOffice** are used to draw diagrams.

### 3.1 Question of sizes and grid snapping in diagrams

Commercial tools for graphical programming have often not a proper answers to this question. Often sizes are scalable in any kind, as the user want to have. Grid snapping is sometimes supported or not, and, sometimes sophisticated algorithm are implemented which avoids lines through blocks and make instead mad ways around all blocks. LibreOffice is here more friendly, it let the user decide about the connection path. This may be only a marginalia.

Let's think about font sizes and grid, requirements:

- In a usual document a proper font size is 9..11 pt, this document uses 9 pt but for A5 page format. A smaller font (pt, 6 pt) is not suitable for reading because of the recognizability of the words and their contexts, it is only for read the package leaflet of medical products.

- A diagram should have place in a document on a A4 or size-B page (~ 18 cm text width). It means the size of a proper view is ~18 x 10..12 cm. Using a whole side in landscape orientation may have a size of 25 x 17 cm, but in landscape mode the document must be rotated only for this page, this is not suitable for reading a PDF document on the screen.

- A diagram has two tasks:

- a) Documentation

- b) Base for the software

For the approach b) the diagram may be well editable as a whole on a large screen, for example with resolution  $2650 \times 1200$  pixel. To document this complex diagram it can be shown in landscape orientation in a document, or better: It should be reduced in

size to fit on a normal page in portrait format. Details are then no longer legible, but important things and orientation should be shown in larger font. Then the overview can be explained and details can be shown as part from exact the same diagram in a higher resolution.

• A common and contradictory question for diagrams is: How comprehensive should it be. Should it contain only one block and some less aggregated ones? Or should it contain the whole truth of a module? The answer of this question depends on the available size for presentation. There should not be to less content.

The UML has the advantage that you can use more as one class diagrams to explain the same class in different contexts. That is a very great advantage and it should be usable also for some Function Block presentations! (Not yet in professional tools). This helps to decide how many content a diagram should contain.

- The readability of a word which is isolated of a sentence, an identifier of a block or line or such one is given also with a smaller font size than 11 pt, especially if it is present in bold font or maybe also in a non proportional font (as for programming language source code). Because in proportional fonts often important small characters such as "il" are to small and bad visible

- For positioning a proper grid size and the **possibility of positioning with cursor keys (!)** is essential. LibreOffice has the property that the step size for the cursor key is anytime 1 mm, independent of other settings. It's

possible use cursor keys for fine positioning (Alt-Cursor...) but this is too fine.

There is a specific property of LibreOffice: The step width by moving with cursor keys is normally 1 mm. You can do fine adjusting in combination with the Alt-key, but this is too fine. If also a grid fine spacing with snap points of 1 mm is selected (a 5 mm grid with 5 fine divisions), then the placing is very proper. All elements are placed in a 1 mm grid, the 1 mm is enough fine for details and enough raw to simple snap in the grid points.

From that, the idea comes to have a standard size of small elements of 2 mm. The mid point is also in 1 mm grid snapping raster. You can have a near distance of lines of 1 mm, well obviously.

To show enough content in a diagram you may use an A3 paper in landscape orientation. On a larger monitor (2560 or 3280 pixel width) it is editable in entire page

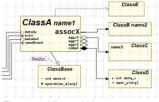

The same content is presented here right side in original magnification. The font size of 6 pt for the most elements is iust readable. It is Consolas bold. The of type names the classes are Arial 8 pt. the name of ClassA is Arial 14 pt. This is a 1:1 presentation. drawn in portrait A4 it is really 1/1 site width.

It means you can have an overview, but you don't see some details in the documentation.

Figure 1: View 40%

If you present the whole diagram in a document in portrait format. is it demagnified to ~ 17..18 cm. it means ~40%. As you see right side, the name of ClassA is readable, also the "assocx" with a font size of 10 pt Consolas bold in the original. Here it is presented with  $\sim 4$  pt because of the demagnification. The others or not readable, but you can recognize the addredations. compositions and associations. The symbols may be obviously though they have a size of only 0.8 mm height.

Parts of the same diagram can be shown in original size, then all is readable.

#### page 12 3 Approaches for the graphic, basic considerations

You should place different approaches of the same module in more as one diagram. This is definitely supported by UML, and should also be usable for function block presentations. In commercial tools such as Simulink it is not possible, but here it is.

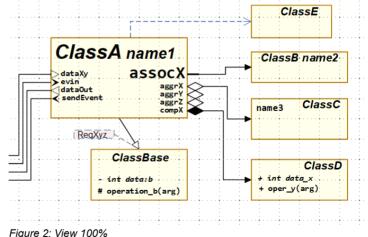

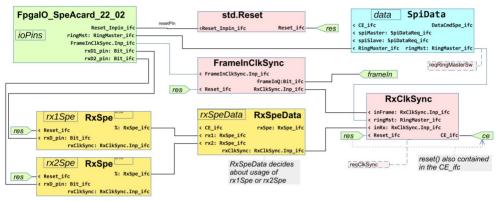

As living example look on the following Class-Object-diagram:

Figure 3: Example for a Module Diagram

This diagram should be well readable in normal view of a pdf viewer. The font and size of the names is consolas 6 pt bold. The original draw area is the width of a A4 page. The pixel solution is  $1351 \times 480$ , results from a Zoom of 200 % on a 1980 pixel width monitor.

The diagram shows a coherence of different blocks to build a synchronized *clock enable*

(ce) in a FPGA. You see two receiver (Rx) modules, which are combined with a third module, with equal light-brown colors. Its a selection of the active input. The output of this third module has the same interface type <code>RxClkSync.Inp\_ifc</code> as the module in the mid. Both are selected from the red right module. With less explanations the coherence should be understandable.

# 3.1 Question of sizes and grid snapping in diagramspage 13

### 3.2 Using figures with style sheets for elements

The first used is a rectangle shape which presents a class or Function Block (FBlock). The rectangle should be marked with the style sheet ofbClass or also ofbFBlock. This style sheet (indirect formatting) associates the semantic to the shape.

A class or FBlock should have a name and a type designation. This can be written either as text in the FBlock (class) shape, as also in an extra shape ofnClassObjName for more free positioning. The text of the ofbFBock is positioned right top in the shape area. Maybe press ctrl-M to remove other automatic formatting informations.

The original UML class diagram has the following approach:

- A class is a rectangle box containing the type name of the class.

- Some data or operations may be named inside the class box, it does not need to be completely.

- All relations to other classes are shown with references to the other classes. This references are often non directed, but sometimes only in a specific direction marked with a little arrow on end. This relations are associations, aggregations, compositions, inheritance, dependencies.

The last point is not mapped to the languages which presents the software which is presented by the UML diagrams. Because: The fact that a class has an aggregation to any other class is a property of the class, and not a property of relations between the classes. It is exactly the same as for data. A data element has a type, and a reference has also a type, the type (or super/basic type) of the referenced class. The name and type of a reference is a property of the class, it is not a property of the relation between the classes.

For that reason the shown relations to other classes are assigned to the class itself.

They are existing also if there is no connection. Then, of course in the implementation it's a null or nil pointer. Or it is just not shown here in this diagram, instead shown in another diagram, but nevertheless it is an element of the class. Look on the images on the page before. There are some not connected aggregations, which may have a meaning on explanation to the diagram.

The elements for connections are named *pin.* This is similar as in Function Block Diagrams where the data connections are presented also as pins.

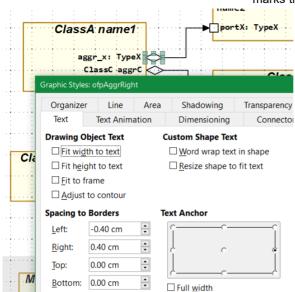

In UML a **port** is known. This is also a pin, see Style\_ofpAggrRight\_TextProp.png Figure1: on next page 15.

The pins are simple small figures with a fixed size, known from UML as the diamond (filled / non filled) for Composition and Aggregation, or they are simple rectangles. The pin contains a text, which is the identifier for the pin and can also contain a type specification, a constant value or also a connection information. The text is written outside left or right from the small pin shape by using the LibreOffice property, that a text can exceed the bounds of the element's graphic. More as that, the left or right margin of the text is set to a value greater or equal the size of the element, and in this kind the text is written outside, left or right next to the element. If you want to have a little more distance, you can also insert spaces left or right of the text. The spaces are removed while evaluation of the text.

Why it is necessary in LibreOffice to set the "Left" value to the negative "Right" value, or also to a higher negative value, otherwise it does not work. It is not consequential. Second, In an older version of LibreOffice it was possible that the Distance value (here "Right") can be greater than the size of the element, to insert a small space right of the shape. From Version ~6.4 this was no more possible, unfortunately. That should be small questions to the LibreOffice community.

Figure1: Style\_ofpAggrRight\_TextProp.png

The pin for connection to the class or FBlock is shown as this small shape or figure. However, it is not the shape itself that

### 3.3 Connectors of LibreOffice for References between classes

The connectors as known from LibreOffice are the proper possibility to connect FBlocks or classes. The connection can be done between pins of the FBlock, or also from/to the FBlock itself.

You can use connectors with orthogonal lines, or straight or curve connectors as if you want.

LibreOffice assigns four connection points ("glue points") to each element by itself. This is sufficient for the pins. It is very simple to connect for example the end point of a diamond of an aggregation with the mid of a port as destination of the aggregation, or also with any other class if the whole class is referenced.

For the larger class block with maybe more connections on different positions you can add some more glue points.

marks the shape as pin for code generation,

the associated style sheet is the essential one. The look of the figure can be changed if desired, it is for human. But the style sheet marks the semantic of the figure. the kind of the element. The settinas in the style sheet. especially the size of the text, can be overridden by direct formatting. This is for larger fonts explained in the chapter before and shown in Figure 1: View 40% page 11. Also the settings in the style sheet can changed be for centralized approach. The name of the style sheet is the important one.

Style sheets are a proven concept for text writing. The direct formatting approach can be also used to a style sheet formatting approach, and both can be combined. A style sheet allows change a formatting style for all

designated elements (paragraphs, parts of text etc.) to achieve a uniform presentation. It is an advantage that is often not enough known. That's for common explanations.

Using connectors between elements in your graphic, the connection remains stable if you move some blocks. You may adjust the inflection points (more precise the mid between inflection). points Some commercial tools such as Simulink try to adjust connections between blocks by itself by sophisticated algorithm, which should avoid lines crossing blocks, and make instead mad ways around all blocks only to avoid crossing a free but reserved area for a name of a block. LibreOffice is here more friendly, it does nothing by itself, only move the connection as necessary, and let the user decide about the outfit of the connection path.

A connector as reference between blocks should have also a Style. If the connected elements are well dedicated by Style

#### page 16 3 Approaches for the graphic, basic considerations

Sheets, you can use the **ofRef** style for all connectors. It produces a small arrow on the end, and a line width of 0.2 mm, nor more.

But there is also a possibility using connectors as in UML. The connectors have especially the start arrow outfit as in UML necessary (diamond for aggregation). Then you can use for the connected elements the common style **ofPinLeft** or **ofPinRight** which does not specify the kind of the element. The connector specifies it. That is the originally approach of UML, also possible here (but not recommended). Both are supported by code generation.

### 3.4 Connect Points for more complex references

Figure2: ReferenceLineCrossesBlock.png

LibreOffice seems to be have the disadvantage that additional inflection points on orthogonal connectors are not possible. Look on the example left side. The connection from aggr2 to port2 through ClassF is not nice. LibreOffice seems to be

Another question is: Having aggregations or other references with one destination and more sources. In UML often there are drawn parallel. But it is more consequently to use a connection

point as it is known from any electrical circuit scheme and also from Function Block Diagrams for data flow. The difference is only: Data flow and electrical schemes has one source and more destination. An aggregation has one destination and can have more sources. The reference line to the connection point is offerferences offerferences offerfaqu offerfecomp offerfcomp offerfcomp offerform offerfunet offerfunet offerfunet offerfunet offerfunet

have the disadvantage that additional inflection points on orthogonal connectors are not possible. Look on the example right side.

The solution is shown also

image. From aggr1 to port1 two connection lines are concatenated. The first line is of type (style) ofrConnPoint, its without arrow on end. Both lines together appears as one line, with proper inflection points.

#### Figure3: OFB/ConnPoint.png

either a simple ofRef which has an arrow on its end, or it is the same as in the image above for concatenation of reference lines, with style or type ofrConnPoint.

### 3.5 Diagrams with cross reference Xref

The cross reference or usual nominated as Xref is an often used symbol to replace too much lines in one graphic, or also to make connections to several sheets of a graphic. The last one should not be in focus here, because on graphic

sheet presents one aspect, spread one diagram over several sheets is not familiar for UML or also Function Block Diagrams.

You may use a Xref for signals and connections, which are well known from name, and which have basically connection meanings (such as "reset") and may be connected to more as one block.

• The figure for the Xref can have any form, but should use the given form (copy it from template). The Style Sheet should be either ofbXrefLeft or ofbXrefRight, whereby the difference is only the text alignment to left or right.

• The name in the Xref symbol should be a mnemonic name for the functionality, valid for this diagram. Here it is a combination of the type of the port and part of name, maybe proper. Figure4: UMLdiagramXrefExample.png Cross Reference usage

• The line from a block to the Xref should be the same type (here a simple ofRef) as without Xref.

• The line from the Xref to the block should have usual the same type, but this is not evaluated. Because the type of connection can be also composition or association the type the here. for association is used is not here. it specificated to the aggregation or composition with the filled or non filled diamond

You can use Xref connections for all line types. The evaluation of the graphic builds a list for all Xref by name per sheet, and checks the connections.

### 4 Working flow creating your own diagrams

First you should load and open the template file from

https://www.vishia.org/SwEng/oofb.wrk/ src/UML\_FB\_DiagramTemplates/odg/ UML\_FB\_DiagramsTemplate.otg

To create a new empty UML class or Function Block diagram you should save this template file under your specific location/name.odg. You should delete the content, the style sheets are not deleted.

Reopen the template file, you need it to copy figures and elements from.

If you have your own file with content but maybe an older version of style sheets, you may copy the style sheets immediately with zip: The odg or otg file is a zip file format. Add the extension .zip and unzip it (simple us the Total Commander). It contains a styles.xml. Replace the styles.xml in your own file (with zip extension). Remove the zip extension and reopen it in Libre Office. It should work. Do not forget to make a backup copy. This is a non documented way, but it seems to be stable since many

years. It works also for OpenOffice in different versions.

#### Look for Grid and Snap

- Open "Tools Options", select "Libre Office Draw" and then first "General". Look for the measurement unit, it should be "cm".

- Then open "Libre Office Draw" and "Grid", look for the proper grid settings (recommended 0.5 cm and 5 Subdivisions because the natural cursor step width is 1 mm. Select "Snap to arid". This is strong recommended. because you have a lot of work for unsnapped blocks and some small inflection points in orthogonal reference lines.

- If you have copied from the template, it should be proper.

#### Create a class or function block:

- Create a simple rectangle in your diagram and assign the style sheet ofnClass. The it gets the yellow color with brown border. Alternatively you can copy a class block from the template.

- Create a simple rectangle and write first your class name into it (press F2 to write text in a selected rectangle). The assign the style sheet ofnClassTypeName to it. Now move the rectangle into the class box, usual (not necessary, but recommended) to the top right border. You should not place the name exact in the mid, it makes a little bit trouble by selecting the correct glue point for the class rectangle.

Alternatively you can copy the rectangle from the template.

Maybe write some data or operations into your class block in the same kind, either by copying from the template, or also by creating simple rectangles and assign the style.

- Then you may copy connections (aggregations etc.). For this you should use the template, copy the correct element in your diagram. On paste it lands on exact the same position as in the template, its on the top spread of the page. You can use the cursor keys to shift it to your destination firstly, so long it is selected. Sometimes the landing position is inside any other stuff, this is а little bit confusina. Unfortunately Libre Office does not paste a figure on the cursor position (as other tools do). It would be more proper.

- You can copy more connection points from the same type also from other ones in your diagram of course, it is usual faster.

- On copying and moving the figures the landing position should be any time in the 1 mm-Grid. Sometimes it may be wrong, you see it on small inflection points and obviously misplaced positions. Then you can press F4, correct the position to even mm. If you have activating snapping, all will be proper after such an adjustment (till a next non obviously positioning which may be also caused by accidentally size changes).

#### Group and ungroup

Meanwhile the detection of content does not need grouping. You can group associated elements (FBlocks with their pins) but you do not need.

The association between elements, FBlocks and pins, is detected by its position. The FBlock frame is responsible, derermines the area. The pins should be inside or at least touch this area with at least on coordinate. In the moment it is a problem if two FBlock frames are too near, should just have a distance of 1 mm.

#### Small problems with movement

#### **Copy connection elements**

The elements have a height of 2 mm and often only a size of  $2 \times 2$  mm. If you select it, Libre Offce shows drag points to change the size, but because the size is not changeable, also a "non possible" symbol. The space for movement is small in the mid of this points.  $2 \times 2$  mm is the smallest size where movement is possible on a 1920-pixel screen with full size width. This is a little bit stupid.

But you can also move with cursor keys.

Using a higher zoom factor (200 % is recommended) ameliorates this situation.

Usual you don't need to see your page margins.

#### Hint: Bring to Back / bring to Front

The rectangle of a class should have a transparency. Then you see also elements which are arranged below (in the back) in relation to the class rectangle. But to work with, the inner elements should be in front and the class rectancle should be in back. Use the menu entry "*Shape - Arrange*" or the context menu with "*Arrange*" to adjust it.

#### **Using layer**

This is not tested yet. Maybe interesting in future.

## 5 Overview capabilities and concepts of the UFBgI

What do the diagram contents mean?

This chapter should discuss some presentations in the ObjectOriented Function Block diagrams in relation to the UML standards and some quasi Standards used for Function Block. Function block representation and UML should not be a contradiction. It should be thought together for the future.

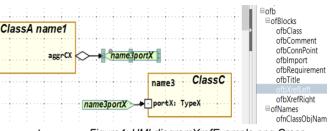

### 5.1 All Kind of Elements with there Style Sheets

The next image shows all given template elements. It is the content of the file

https://vishia.org/fbg/deploy/UFBgl DiagramTemplate.odg

#### Figure5: odg/UFBgl\_DiagramTemplate.png

Right side you see some style sheets. You can use this image (given in the file UML\_FB\_DiagramsTemplate.odg) to pick an element, copy it to clipboard and insert it in your graphic. The style sheets are copied by opening this file and save it with your name. Unfortunately LibreOffice does not allow loading style sheets from another given odg document, only by copying the original one (see also <u>https://ask.libreoffice.org/t/howcan-i-import-styles-from-other-drawdocuments/8834</u>).

But you can copy the internal style.xml file from the UML\_FB\_DiagramsTemplate.odg zip archive. This is a simple, proven workflow that has not been recommended as often, but it works:

- \* Copy the original UML\_FB\_DiagramsTemplate.odg file to UML FB DiagramsTemplate.odg.zip

- \* Open the zip file by a unzip tool.

- \* Copy the internal styles.xml for your own.

- \* Make a backup from your own **\*.odg** file only to have it for trouble.

- \* Rename your own \*.odg file to \*.odg.zip and open it with a zip tool.

- \* Replace the internal styles.xml with the styles.xml from the template.

- \* Rename your own \*.odg.zip file back to \*.odg

- \* Check if all is proper. It should be.

For dealing with zip content, using the Total Commander is a good decision.

The class in the mid with **name: ClassTypeA** contains all connection elements for the concept described in 3.2 Using figures with style sheets for elements page 14. The identifier of the style sheet is here used also as name, only for documentation.

The class left **ClassType name** contains simple connection elements of the base style **ofPinRight** and **ofPinLeft**, but using connections with the specific type. Their style names are shown here as pin names. This was a first concept, maybe in future not recommended. Here the connection styles determines the kind of the pin.

The figure outfit is proper for view, but not necessary for content. It is also possible to use simple rectangles with the proper style. Then it is not so good recognizable which kind of pin it is. But handling of content (the text) more proper. is lt mav be recommended to use this simple rectangle forms for the amount of data pins, and use the specific form with the triangle shape for the events to see what's happen. This is in the moment growing experience. The evaluation of the graphic works with both

variants, because for evaluation only the associated style is essential, not the form.

The internal data of a class can be shown. as usual in UML, with the style ofnData. The designation about private, public, protected should be written with a first character - + # as usual in UML. Writing the type of the data is recommended. The operations can be written with their argument names, if it is more informational. The operation itself, its body, should be define anyway in a programming code and not with a diagram. association between the shown The operation in a diagram and the real operation is only for documentation, should not be formalistic.

For the documentation blocks the style ofbComment should be assigned. A requirement is presented also usual in UML with a short identifier. It is written in a ofbRequirement rectangle block. The connector between ofbComment and ofbRequirement has the style ofRefDocu. If you copy this connectors from the template, you get also the style reference.

This diagram contains also data and event flow. This is described in chapter Error: Reference source not found.

### 5.2 FBlock or class, name and type

The name of a FBlock and the type can be written in the text of the rectangle shape for **ofbFBlock** which is used for the FBlock, and also for a class in UML thinking. The original style of **ofbFBlock** expects the text in the right top corner, see Figure6: But sometimes this works not properly, then either "*Format* – *Clear direct Formatting*" on the shape helps, or Menu "*Format* – *Text Attributes*" and adjust it. You can use also the direct formatting to put the name and the type in the mid, to another corner, or at a desired position. But right top is often a good decision because the FBlocks have often more inputs (left side) then outputs.

- By the way, inputs do not need positioned left, can be also right or rotated on top or bottom, same as outputs. The drawing style have more possibilities than some commercial tools, you can use it for your own.

The other possibility for name: type is a text field marked with the style ofnClassTypeName. This text field can be positioned anywhere inside or touching your FBlock shape.

### 5.3 Show same FBlocks multiple times in different perspectives

There is an interesting and important principle using in UML class diagrams. A class can be presented in more as one perspective in several diagrams, and also more as one time in one diagram. The class is presented by its name, it is able to found in the repository of the UML data. The diagrams plays only the role of presentation of the class with its properties just in several perspective.

In opposite, traditional Function Block Diagrams shows one FBlock as one instance. Often the FBlock does not need a specific name, then it is automatically named

| Graphic Style      | s: ofbFBlock |       |                  |              |

|--------------------|--------------|-------|------------------|--------------|

| Organizer          | Line         | Area  | Shadowing        | Transparency |

| Text               | Text Anima   | ation | Dimensioning     | Connector    |

| Drawing Ol         | oject Text   | c     | ustom Shape Text |              |

| Fit wic            | Ith to text  |       | Uord wrap tex    | t in shape   |

| 🗌 Fit h <u>e</u> i | ght to text  |       | Resize shape to  | o fit text   |

| <u> </u>           | rame         |       |                  |              |

| <u>A</u> djust     | to contour   |       |                  |              |

| Spacing to         | Borders      |       | Text Anchor      |              |

| <u>L</u> eft:      | 0,00 cm      | -     | Q(               | •            |

| <u>R</u> ight:     | 0,05 cm      | -     | 0 0              |              |

| <u>T</u> op:       | 0,05 cm      | •     | 6                | d            |

| <u>B</u> ottom:    | 0,00 cm      | •     | Full width       |              |

Figure6: odg/ofbFBlock-TextStyle.png

If you want to describe only the class (type), then you need to write **:typeIdent** with the colon. This is not UML-conform, but unique.

If you omit the type name, but the classification of the named instance is done in another FBlock with the same name, it is admissible. It may simplify the diagrams. If the type is never associated, an error message is given on translation.

This approach uses the principle, showing also a FBlock in several perspectives, in opposite to traditional FBlock diagrams, but similar as UML. It means, on FBlock as one instance can be shown more as one time in the same diagram or in several diagrams related to the same module. The FBlock is dedicated by its name. Drawing a second FBlock with the same name is the same instance.

This principle enables showing complex large FBlocks in several perspectives. Different connections are shown on different places, also the same connection can be shown more as one. For example inputs of one functionality of a FBlock are shown on

#### 5.3 Show same FBlocks multiple times in different perspectives

page 23

one page with focus of that input signals, other input signals are shown on a second page, and the output connections and processing are shown on a third one. Also the connections are unique dedicated by its pin name on the named FBlock with the named type. This offers more overview. The dispersion of one FBlock connectivity in several views mav be seen as disadvantage, it becomes confusing. But notice, there are search operations and evaluations of the graphic which gives an overview to find all locations of the same FBlock instance. The idea is newly for FBlock diagrams, look for its advantage.

Now this idea is also usable for the class description idea: Any FBlock instance is dedicated by its type. The type is the class type. All occurrences of the same type of Flocks are properties of its class. Also FBlock with only the type name, without instance name presents the class properties. The sum of all is the property. This is true for the type of a c FBlock which is a class as also for the connectivity of an instance of a FBlock in several graphic presentations.

Look for example to Figure7:in the next chapter. The FBlock with name h3p is assigned to the type BpParam, left bottom. But this block is drawn twice, the second is magenta, has not the type identification because the name is unique, and shows the instance with another event input ctorObj and some other data. This is another functionality associated to this instance, and also to the same class.

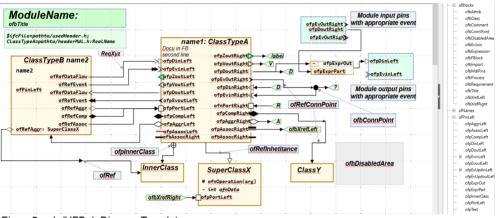

# 5.4 Function Block and class diagram thinking in one diagram and the ObjectOrientation and also Functional aspect

One of the basic ideas of this approach is just, join UML thinking and FBlock thinking. UML presents in class diagrams relations between classes. A class is an abstraction of implementation. The implementation uses instances (of classes). In opposite, ordinary Function Block Diagrams only work with instances. A "class" is an unused word in this way of thinking. But in fact, using a Function Block type from a Library is *"instantiation of a class"*, the library block type is the class.

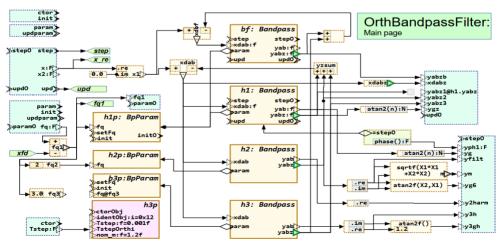

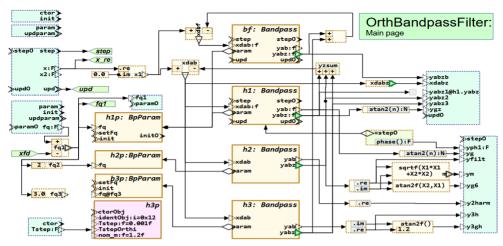

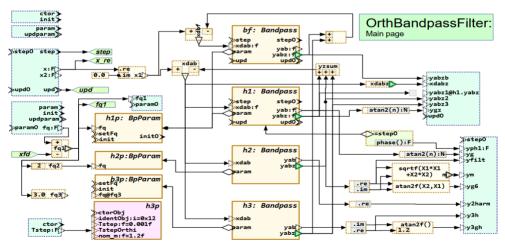

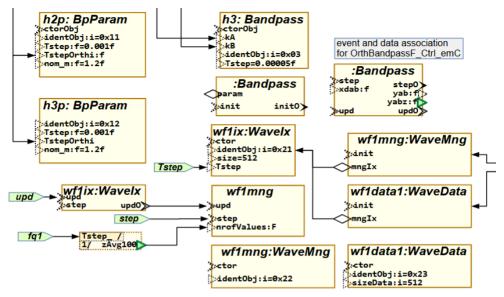

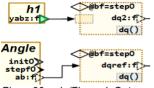

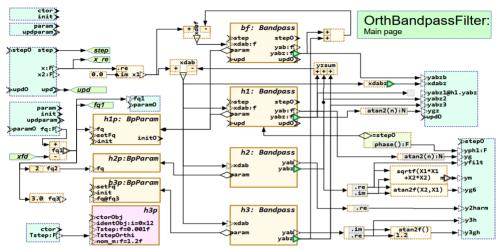

Figure7: odg/OrthBandpassFilter.odg.png

Figure8: odg/OrthBandpassFilter.odg.png

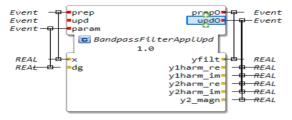

Figure8:odg/OrthBandpassFilter.odg.png shows primary a Function Block Diagram (FBlock diagram). The green parts are the input and output pins of the module. Some FBlocks presents expressions, these are with dashed lines. The other FBlocks presents instances (each three from the same type) which are connected with data flow.

But from the Bandpass FBlocks to the BpParam FBlocks there are aggregations. That shows two things:

- a) There is an aggregation from the type (class) Bandpass to the class BpParam.

This is a relation of a class diagram.

- b) The aggregation from bf and h1 is initialized to refer h1p, as also h2 refers h2p and h3 refers h3p. This is a property of the FBlock instances.

The relation shown with the aggregation can be seen also as data flow, but in the opposite direction. Initially the address of the h1p FBlock is provided to the bf and h1 FBlock, to refer it, adequate for h2 and h3. Hence, the diagram contains information about class (or type) relations as class diagram and information about instance relations as Function Block Diagram with data flow. The combination in thinking of FBlock instances, its type (the class) and several operations, here presented by the several events is a kind of ObjectOriented thinking. The "Object" is the instance of a well defined type, the type (class) has some properties valid for all Objects of this type, and it has operations.

The last one aspect, given operations, is also shown in the green block right mid with phase():F. This is a shape of style ofbExpression but with an aggregation. It means the expression aggregates a FBlock instance, which are the data for the given operation in the expression, and hence the operation is associated to the data type, it is an Object Orientated operation (or method as often named). The second specifity is, this operation should not have side effects, it does not change data in the aggregated obiect. because it is designated as expression term. This is an important feature Functional Programming, of and unfortunately not so much considered in Object Orientation, but important. In C++ implementation this is an operation ending with const after the closing parenthesis if the function definition line:

float Bandpass::phase() const {...}

but for example in Java it has not a proper counterpart, Java does not know a designation for const operations, unfortunately. (It is not the final keyword!).

In opposite, operations which change data should be present as FBlock with the

adequate event. The event characters the operation, as shown on all FBlocks, especially the three different operations shown in two FBlocks h3p left bottom. Note that setFq(float fq) and init(float fq) are defined in the same FBlock, only possible in combination with init.

### 5.5 More as one page for the FBlock or class diagram

The chapter above 5.4 Function Block and class diagram thinking in one diagram and the ObjectOrientation and also Functional aspect allows simple to disperse a diagram over a lot of pages (as necessary) because the same FBlock instance can be shown for example with its input signal wiring, and on another page with its output signals, or group of signals. This allows formally descriptions more near to explanations. One Image (one side) should present one aspect. Which – this is document- or explanation oriented. Data flow connections can also be joined by Xref blocks.

Figure9: ofg/ofbTitle-1.png

Any page need have a title block, of style **ofbTitle**. It contains the name of the module and a short text what it contains.

The pages can contain several modules. The association of module diagrams to files.odg is an important topic. If you have related modules, you can store all it in one file. On the other hand it is possible to have more as one file for one module. This should only be regarded while translation the module.

### 5.6 Using events instead sample times in FBlock diagrams

Usual for FBlock diagrams sample times are familiar. It follows from the basic approach that the FBlock connections are executed cyclically. That is so in some applications. for example industrial automation control. But sometimes events also play a role. In ordinary automation control often this is regarded by polling (quest of input signals) in a cyclically kind, because their basic operation system supports firstly cycles. The importance of events was often not the focus when such systems were created, although events were common and wellknown in other areas of software technology. For example Simulink works basically with "sample times" but has specific opportunities ("triggered subsystem") to deal with events.

Well, the assignment of signals and FBlocks to events *includes working with sampling times*, but also triggered operations. More as that, the *event flow presents* better as a data flow the *execution order of FBlocks*. Only using the data flow sometimes it is not well as necessary predicted. If the execution order is internal information (the user does not see it unless you study the generated source code), then uncertainties remain.

The UFBgI tool allows the automatic derivation of the event flow from the data connections (data flow). The event flow is shown in the textual representation of the graphic and can be viewed or analyzed. It is also possible to determine a specific event connection in the graphic by the user.

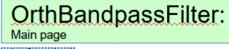

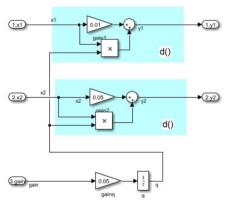

Figure10: OFB/DataFlowPID4.png

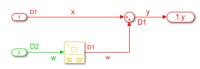

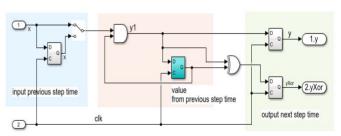

The Figure10:OFB/DataFlowPID4.png is an example primary as Function Block diagram with a **data flow**. The **event flow** shown in gray is not necessary to be drawn. Here it is only shown in gray what is automatically generated. But the **event pins** should be determined as shown (**drawn black**). With the given event pins the data are related to the events, instead to "sample times". Here the x ist related to step, and the w to

stepslow. The reference value w comes from another sample time or just with another event. The data flow from x to the output yCtrl is given, hence yCtrl is related to the step event chain and it is delivered with the step0 output event. The value stored in the w1 variable is a "state value" set with the stepSlow event and only used, similar as after a "Rate Transition" in Simulink. But this image has also an **Aggregation** from the **PID** controller FBlock to its Parameter FBlock. This is **UML**. In Runtime, the address of the parameter instance is delivered to the **ctr1: PID** one time on initializing the system. It means that is a **data flow** from **ctr1p\_ Param\_PID** to **ctr1: PID** revers to the aggregation line.

The green blocks of style ofbMdlPins are responsible to determine the module pins from/to outer or just the type of the module. Each ofbMdlPins block is responsible to associate event-data relations (as also familiar in IEC61499 diagrams), but additionally the also update pin is associated here:

It means that the input variable x is bind to the input event step. It presents the step() operation (should be called cyclically in the step or sample time). Because the x is forwarded by data flow to the ctrl: PID, also the event step is forwarded. Due to the interface definition of the PID type the input dwx is associated to the PID event input step. Hence the data flow  $x \rightarrow ctrl.dwx$ determines also an event flow from step  $\rightarrow$ ctrl.step.

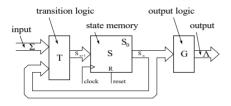

The role of "*update*" comes from the mealy and moore automate thinking for logic and it is also familiar in numeric solutions for control: All values are first prepared. Preparation uses always the values from the step time before (or in binary logic preparation of D inputs of Flipflops uses only values of the Q outputs of the clock cycle before). That is the ordinary role of the step event.

The update event now realizes the switch of all state values (or clock for Q in Flipflop logic) from the old to the current step to use for the next step. In a sample or step time of a controlling logic first all modules executes the prepare event which is here named step. If all parts have been prepared, then the update comes. This assures exactly working for solutions of differential equations and typically for controller theory, it is the Euler principle for numerical integration.

A FBlock can also propagate output values with the prepare event, it depends from the functionality. In Simulink as similar solution an input of an S-Function can be designated as

**ssSetInputPortDirectFeedThrough(port,1)** if it influences an output or not (set to 0, default).

In this example shown the output y.ctrl is set newly with the ctrl.upd event. Hence an event connection between ctrl.upd and upd of the module accompanies the data flow from ctrl.y to the modules yCtrl output. The relation between step, step0, upd, upd0 in the PID FBlock type is clarified by the class definition of PID.

Next you see a code snippet of the textual representation of this module in IEC61499, see next chapter:

```

FUNCTION BLOCK CtrlExample

EVENT INPUT

param WITH Td, Tn, Tsd, kP;

run;

stslow WITH w;

. . .

END EVENT

EVENT OUTPUT

step0 WITH yCtrl;

. . .

VAR INPUT

Td : REAL;

Tn : REAL;

. . .

VAR OUTPUT

vCtrl : REAL;

END_VAR

FBS

ctrl : PIDf_Ctrl_emC;

ctrlp : Param_PID;

w1 : Expr FBUMLg1( expr:='+;;' );

wxd : Expr_FBUMLg1( expr:='-+;;' );

yCtrl : Expr FBUMLgl( expr:='+; ...

END FBS

EVENT CONNECTIONS

run TO ctrlp.run;

stslow TO w1.prep;

updslow TO w1.upd;

step TO wxd.prep;

END CONNECTIONS

DATA CONNECTIONS

Td TO ctrlp.Td; (*dtype: F *)

Tn TO ctrlp.Tn; (*dtype: F *)

```

### 5.7 Storing the textual representation of UFBgl in IEC61499

It is interesting and promising that the widely FBlock programming proven in the IEC61131 standard for industrial automation control (tools such as Siemens Simatic FBD in TIA-Portal or Beckhoff Codesys) has been further developed to the IEC61499 standard. This development was started in ~2006. Also Siemens was one of the driver in that time. The IEC61131 is used since many years for automation programming. The IEC61499 is standardized and used, but not from the global meaningful players. they only monitors this development. The reason (in my mind and experience) is not disadvantages of IEC61499, it is more a too widely usage, supporting and maintenance of the long term existing IEC61131.

The IEC61499 has introduced an event coupling between function blocks. This determines the stepping order better than the ordinary net lists in IEC61131, but it allows also to distribute the implementation of one Function Block Diagram over several automation stations. Event connections between distant stations forces communication automatically network implementation and assures the correct order of execution in the dispersed station. without additional effort. That's the advantage for automation programming. But the more universal character of event coupling inclusively state machine thinking can also basically used for embedded control programming.

which can be called either cyclically (for step time driven thinks) of also from the state behavior or independent for example on user accesses.

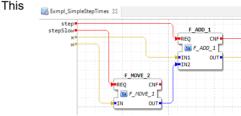

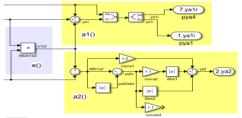

But the drawing of the event connections in a IEC61499 diagram is an additional effort. The image shows an example with event coupling for simple data relations with the graphical edition tool 4diac. In most cases an event flow (chain) is also determined by the data flow. Evaluation of the data flow results in an event connection, which should not be drawn manually. It is automatically detected during the evaluation of the graphic, and stored in the data model. Only if dedicated event relations are necessary, the events should be drawn in graphic.

The IEC61499 standard is used to store the content of UFBgI diagrams in textual form. This allows also a proper comparability if details in the diagrams are changed. That is a high importance to use this tooling in the development of software, a proper traceability of changes is necessary. With pure graphics, this is often not properly supported, one of the reasons for the still widespread use of textual programming.

It is also possible to read this stored IEC61499 textual files for processing for sub modules, and for code generations, as well as reading IEC61499 fbd files from other tools to merge here.

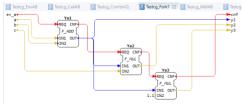

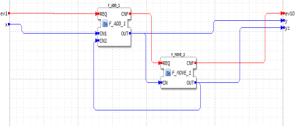

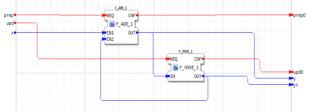

Figure11: 4diac\Testcg\_Fork1.png

A chain of events in the same implementation platform (same thread in a CPU) defines a statement order. Different event chains are related to operations,

### 5.8 Source code generation from the graphic

As is usual with some FBlock graphics, code generation from the graphic is a prerequisite for being able to work productively with it. This chapter should only give an overview. Refer for more opportunities in chapter ToDO

The evaluation of the graphic is done with a Java command line process as (shortened)

```

java -cp tools/vishiaBase.jar;

```

```

... tools/vishiaFBcL.jar

```

```

... org.vishia.fbcl.Ufbconv

```

```

... -dirGenSrc:src/UFBglExmpl/cpp/genSrc

```

```

... src/UFBglExmpl/odg/OrthBandpassFilter.odg

```

This reads the graphic, writes anyway a IEC61499 fbd file, and writes here C-language header and implementing code.

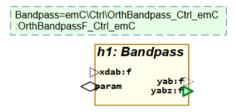

The graphic is shown (as part, one page) in Figure7:odg/OrthBandpassFilter.odg.png. The generated code looks like (shortened)

```

/**Generated by org.vishia.fbcl. made by ...

#ifndef HGUARD_OrthBandpassFilter

#define HGUARD_OrthBandpassFilter

#include <emC\Ctrl\OrthBandpass Ctrl emC.h>

```

typedef struct OrthBandpassFilter\_T {

```

struct { // Locale struct for all din

float x; // OrthBandpassFilter.x

float x2;

float fq;

} din;

struct { // Locale struct for all dout

bool initOk;

....

```

```

} dout;

```

float\_complex xdab; // Expression xdab

```

OrthBandpassF_Ctrl_emC_s h1; // h1

Param_OrthBandpassF_Ctrl_emC_s h1p; // h1p

OrthBandpassF_Ctrl_emC_s h2; // h2

```

```

} OrthBandpassFilter s;

```

```

void step_OrthBandpassFilter ( );

void upd_OrthBandpassFilter ( );

...

```

#endif

The implementation file is generated as:

There are some stuff which is regarded beside the event flow and hence the execution order. The types of all elements are forward and backward propagated. For the here used complex data types the operations are duplicated respectively specific functions are created, and so on.

The code generation is controlled by textual template files using the java class OutTextPreparer, see

Any user can proved its own templates for code generation, can copy the originals and modify, or can write its own template for other languages or only specific style guides. For pure C language an object oriented style is used of course to represent the instances of classes. classes are presented by struct { } with its associated operations with a thiz reference to the own struct. This can be encapsulated also by C+ +.

### 5.9 Run and Test and Versioning

Only yet minutes:

- \* Compilation in a PC platform (Visual Studio, Eclipse CDT, ...

- \* Environment for running in C/++ as given (familiar for C development)

- \* Physical simulations cannot be done, maybe as future development.

- \* But coupling with another Simulation tool for physics is very recommended, use your own tool. Can bei Simulink, Modelica, or what ever.

- \* The coupling should be always possible with shared memory on the same PC. For Simulink such an SharedMem Sfunction block, configurable due to a header file on the counterpart, is existing since ~2021, aks me. Should be documented also here.

Versioning:

- \* Store the odg graphic

- \* Store the IEC61499 textual representation for compare which changes.

- \* Store the generated sources in the target language "Secondary Sources".

One of the important capabilities is the generation of code in a proper target language. The other approach is: storing the graphic in a unique proper readable textual representation. The advantage of that is: The content of the graphic is comparable between progress of development (versions). Whereby not the graphic appearance is in focus (better seen in original graphic), but the content for functionality and code generation.

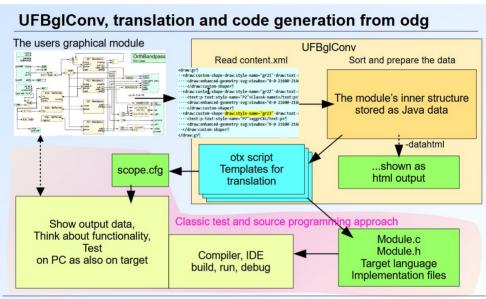

To have an overview look on the following image:

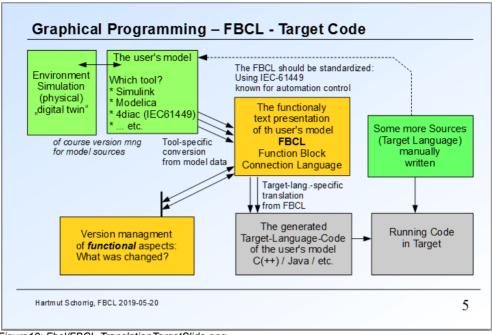

Figure12: Fbcl/FBCL-TranslationTargetSlide.png

This is an older image from 2019, but it shows the whole truth. The so named FBCL (Function Block connection language) is here shown as textual representation of the graphic, whereby here the usage of Open/LibreOffice for the graphic was not yet present. But the using of IEC61499 was already found as coding standard for the textual graphic representation. This figure shows also the topics of simulation of the functionality shown in the graphic, also including usage of manual written (core) sources in the target language.

# 6. Details

# **Table of Contents**

| 6. Details                                                            | 32 |

|-----------------------------------------------------------------------|----|

| 6.1 Data types                                                        | }4 |

| 6.1.1 One letter for the base type:                                   | }4 |

| 6.1.2 Unspecified types:                                              | 35 |

| 6.1.3 Array data type specification3                                  | 86 |

| 6.1.4 Container type specification                                    | 86 |

| 6.1.5 Structured type on data flow3                                   | }7 |

| 6.1.6 Data type forward and backward propagation3                     | 8  |

| 6.2 One Module, Inputs and Outputs, file and page layout4             | 10 |

| 6.2.1 Module in file organized in pages4                              | 10 |

| 6.2.2 Module pins4                                                    | 10 |

| 6.2.3 Order of pins                                                   | 2  |

| 6.2 4 The module's output4                                            | 13 |

| 6.3 Possibilities of FBlocks4                                         | 14 |

| 6.3.1 Difference between class, type and instance4                    | !4 |

| 6.3.2 FBlocks for each one function, data – event association4        | 15 |

| 6.3.3 Aggregations are corresponding to ctor or init events4          | 16 |

| 6.3.4 FBlocks for operation access in line in an expression - FBoper4 | 17 |

| 6.4 Expressions inside the data flow5                                 | 50 |

| 6.4.1 Expression parts as input5                                      | 50 |

| 6.4.2 More possibilities of DinExpr5                                  | 51 |

| 6.4.3 Any expression in FBexpr5                                       | 54 |

| 6.4 4 Output possibilities5                                           | 54 |

| 6.4.5 Set components to a variable5                                   | 55 |

| 6.4.6 Output with ofpExprOut5                                         | 55 |

| 6.4.7 FBexpr as data access5                                          | 6  |

| 6.4.8 Type specification in expressions5                              | 6  |

| 6.4.9 FBoper, operation for a FBlock5                                 | 57 |

| 6.4.10 FBexpr capabilities compared to other FBlock graphic tools5    | 57 |

| 6.5 Connection possibilities5                                         | 58 |

| 6 | 6 Drawing and Source code generation rules                                    | . 60 |

|---|-------------------------------------------------------------------------------|------|

|   | 6.4.1 Writing rules in the target language used from generated code from UF   | _    |

|   | 6.4.2 Life cycle of programs in embedded control: ctor, init, step and update |      |

|   | 6.4.3 Using events in the module pins and FBlocks, meaning in C/++            | .62  |

|   | 6.4.4 More possibilities, definition of special events                        | . 64 |

| 6 | 5 Converting the graphic – source code generation                             | . 66 |

|   | 6.5.1 calling conversion with code generation                                 | . 66 |

|   | 6.5.2 Templates for code generation                                           | . 68 |

### 6.1 Data types

# **Table of Contents**

| 6 | .1 Data types                                    | 32 |

|---|--------------------------------------------------|----|

|   | 6.1.1 One letter for the base type:              | 32 |

|   | 6.1.2 Unspecified types:                         | 34 |

|   | 6.1.3 Array data type specification              | 34 |

|   | 6.1.4 Container type specification               | 34 |

|   | 6.1.5 Structured type on data flow               | 35 |

|   | 6.1.6 Data type forward and backward propagation | 36 |

In the Figure10:OFB/DataFlowPID4.png the input x:F is designated as float input with the letter F. This is very space-saving but still obvious. Other tools sometimes have only a "Pin dialog" where the type can be selected and can optional show the type in the graphic, but then all types destroying the overview. The idea only using one character should be seen as proper, the number of types used are not too much. This is for the standard usual numeric types. The type of aggregations are determined bv the destination class. A type name can be given additionally if necessary.

The problem on numeric and basic types is: There are a lot of designations in different programming languages and usages, but they are similar. A second approach is: Also regard non full deterministic types.

#### 6.1.1 One letter for the base type:

IEC61499 and also the automation system programming language IEC61131 knows the following definition of types, See *IEC* 61131-3 Second edition 2003-01, Reference number *IEC* 61131-3:2003(*E*), page 32. The type **CHAR C** was later defined in IEC61131.

| ANY                        | Α           |

|----------------------------|-------------|

| +-ANY_DERIVED              | L           |

| +-ANY_ELEMENTARY           | E           |

| +-ANY_MAGNITUDE            | M           |

| +-ANY_NUM                  | N           |

| +-ANY_REAL                 | G           |

|                            | F           |

| REAL                       | D           |

| +-ANY_INT                  | ĸ           |

| LINT, DINT, INT, SINT      | JISB        |

| ULINT, UDINT, UINT, USINT  | <b>ουων</b> |

| +-TIME                     | Т           |

| +-ANY_BIT                  | b           |

| +-LWORD, DWORD, WORD, BYTE | quwv        |

| +-B00L                     | z           |

| CHAR                       | c           |

| +-ANY_STRING               |             |

| STRING                     | c           |

| WSTRING (not specified)    |             |

| +-ANY_DATE                 | н           |

| DATE_AND_TIME              | t           |

| DATE, TIME_OF_DAY          | a h         |

|                            |             |

Complex types, not defined in IEC61499

| ANY_MAGNITUDE      | м   |

|--------------------|-----|

| +-ANY_CNUM         | n   |