(empty first page)

# OFB – Implementation – chapter 8

Dr. Hartmut Schorrig www.vishia.org 2024-10-09

### **1** Inner Functionality of the Converter Software

This first level chapter should show the inner functionality of the converting software to read Open/LibreOffice diagrams, translate to and read IEC61499, and generate source code in the target language.

### **Table of Contents**

| 1 Inner Functionality of the Converter Software                                         |              |

|-----------------------------------------------------------------------------------------|--------------|

| 1.1 Data Model data classes                                                             |              |

| 1.1.1 FBtype_FBcl                                                                       |              |

| 1.1.2 FBlock FBcl                                                                       | 8            |

| 1.1.3 Pin_FBcl and PinType_FBcl                                                         |              |

| 1.1.4 Write instances for FBlock_FBcl, FBtype_Fbcl, Module_FBcl                         |              |

| 1.1.5 FBexpr_FBcl: FBlock for expressions, presentation in FBlock_FBcl                  |              |

| 1.1.6 Module with FBlocks                                                               |              |

| 1.1.7 DType_FBcl and DTypeBase_FBcl                                                     | 14           |

| 1.1.8 Event tree node                                                                   |              |

| 1.2 Reading graphic files from different inputs, UFBglConv                              | 18           |

| 1.2.1 Complete a module                                                                 |              |

| 1.3 Read data from LibreOffice odg files                                                |              |

| 1.3.1 The file format of odg – content.xml                                              |              |

| 1.3.2 Read content.xml from the odg graphic file to internal data                       |              |

| 1.3.3 Sorting XML data to Shapes for each page                                          |              |

| 1.3.4 Gather data for OdgModule page by page                                            |              |

| 1.3.5 Build the data in FBcl data                                                       |              |

| 1.3.6 Connect all FBcl pins due to connection of graphic pins                           |              |

| 1.3.7 Preparation of Expressions from odg                                               |              |

| 1.4 Read data from Simulink                                                             |              |

| 1.5 Read data from IEC61499 text files (fbd)                                            |              |

| 1.6 Complete Preparation of the module                                                  |              |

| 1.6.1 Forward and backward propagation of data types                                    |              |

| 1.6.2 Identification of the event flow due to data flow                                 |              |

| 1.6.3 OFB: Build the event chain                                                        |              |

| 1.6.4 Completion of condition events                                                    |              |

| 1.7 Code generation due the to event flow                                               |              |

| 1.7.1 Using a templates for code generation with OutTextPreparer                        |              |

| 1.7.2 Tracking the event chain for a module's operation                                 |              |

| 1.7.3 Access operation to dout, arguments                                               |              |

| 1.7.4 Conditional events in the operation                                               |              |

| 1.7.5 Code generation for one FBlock, one line or statement in the chain                |              |

| 1.7.6 Expression to set elements in a variable                                          |              |

| 1.7.7 Set the module output                                                             |              |

| 1.7.8 Code generation for FBexpr                                                        |              |

| 1.8 All links to related documents                                                      |              |

| t may be not only for deep experts; Also if you on Java-8, or Open-Jdk), with           |              |

| and this inner stuff you can better understand — librariae without additional librariae | - The vietic |

It may be not only for deep experts; Also if you see this inner stuff you can better understand the concepts.

Generally all this converter software is written in Java. Only a standard Java is used (based on Java-8, or Open-Jdk), with is standard libraries, without additional libraries. The vishia basic library **vishiaBase.jar** is used. This library contains all basic functionality for example to read XML.

#### 1 Inner Functionality of the Converter Software

You find some information about the vishiaBase.jar in <u>https://vishia.org/Java</u>

The sources for the vishiaBase.jar and for the vishiaUFBg1.jar are able to download as zip beside the jar files itself (https://vishia.org/Java/deploy/, the version archives are hosted on https://github.com/JzHartmut

You can translated and executed the sources for example in an Eclipse environment, in debug mode.

This first level chapter should contain enough hints to navigate in this sources. Some javadoc links are contained here. Also the sources with its generated javadoc contains explanations of the classes and operations.

### 1.1 Data Model data classes

### **Table of Contents**

| 1.1 Data Model data classes                                            | 6  |

|------------------------------------------------------------------------|----|

| 1.1.1 FBtype FBcl                                                      |    |

| 1.1.2 FBlock_FBcl                                                      |    |

| 1.1.3 Pin_FBcl and PinType_FBcl                                        |    |

| 1.1.3.1 PinType_FBcl                                                   |    |

| 1.1.3.2 Association between Event and Data Pins                        | 9  |

| 1.1.3.3 Associaton between Input and Output pins                       |    |

| 1.1.3.4 Association between prepare and update events                  | 9  |

| 1.1.3.5 Multiple pins                                                  |    |

| 1.1.3.6 Operations or Actions assigned to the Pins, code generation    |    |

| 1.1.4 Write instances for FBlock_FBcl, FBtype_Fbcl, Module_FBcl        |    |

| 1.1.5 FBexpr_FBcl: FBlock for expressions, presentation in FBlock_FBcl |    |

| 1.1.6 Module with FBlocks                                              |    |

| 1.1.7 DType_FBcl and DTypeBase_FBcl                                    | 14 |

| 1.1.7.1 Using DType FBcl                                               | 14 |

| 1.1.7.2 Using DTypeBase_FBcl                                           |    |

| 1.1.8 Event tree node                                                  |    |

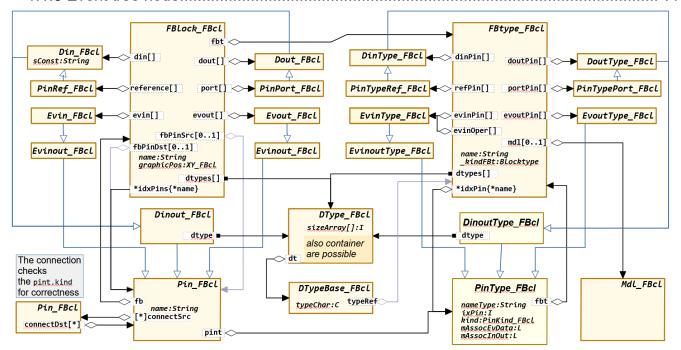

Figure 1: FBcl/FBlock\_FBlockType\_Pin\_omd.png Overview class diagramm FBlock FBtype, Pin\_FBcl

The diagram Figure shows the relation between Instances of FBlocks and its Types and Pins. The FBlocks are the base elements of the Function Block Diagrams. and also for UML class diagrams. A class is presented also with a <u>org.vishia.fbcl.fblock.FBlock\_FBcl</u> (www) because of its interconnections.

This diagram Figure shows the pins of Blocks and their types only on the example of data input pins. The other pin kinds are similar.

### 1.1.1 FBtype\_FBcl

The class <u>.../fblock/FBtype\_FBcl</u> (www) presents a FBlock Type. There are some standard types such as for expressions, event join or rendezvous of events (E\_REND in IEC61499) and variable storage (F\_MOVE in IEC61499) and for compatibility all known standardized FBlocks of the IEC61131 norm (automation control, PLC = Programmable Logic Control).

All functionality which is immediately given in C/++ language for embedded control can be wrapped with a FBlock\_Type\_FBcl to embed it in a graphic. The FBlock type definition can be written manually in textual form using the IEC61499 coding (fbd file), or also designed in a LibreOffice graphic (odg, OFB diagram).

Specific **FBlock\_Type\_FBc1** on user level can be defined graphically with OFB graphic. It can be stored as fbd file due to the IEC61499 standard.

The Java class FBlock\_Type\_FBc1 presents the interface data of this FBlock types. The content (inner functionality) is either given immediately in C/++ or the appropriate destination language, or it is contained in a Module\_FBcl, see Java class ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock/Mo dule\_FBcl.html (www).

The FBlock\_Type\_FBcl has 6 arrays which describes the Pins:

- dinPin : <u>DinType\_FBcl</u> (www):

- doutPin: <u>DoutType\_FBcl</u> (www)

- evinPin: EvinType\_FBcl (www)

- evoutPin: EvoutType\_FBcl (www)

- refPin: <u>PinTypeRef\_FBcl.html</u> (www)

- portPin: <u>PinTypePort\_FBcl.html</u> (www)

The data and event pins are also defined in IEC61499. The **refPin** is an aggregation to another FBlock, as source pin (as in UML). The counterpart is the **portPin**, which is a destination pin. In Uml either it is a really port (any inner instance reference in a FBlock), or it is **THIS**, which presents the whole referenced FBlock.

For IEC61499 presentation (fbg, FBcl source file) the refPin is mapped to a dinPin, arranged after the other dinPin as input. On runtime the reference value will be set in the initialize phase with the init event. The data flow is reverse to the UML presentation as reference to the other instance or type. Adequate it is with the portPin is mapped to a doutPin because it delivers as output the reference. The type of this dinPin and doutPin are always designated in the IEC61499 files as <:::name.>\_\_REF whereby <:::name.> is the name of the FBtype\_FBc1.

The constructor FBtype FBcl(kind, name, module, OFB-project) (www) gets only the name and the module where the FBtype FBcl is member on. The module is adequate the package in UML. The kind is only used the distinguish between some basically functionality. The OFB-project is used only for creation a proper DType FBcl as data type for the instance itself. stored in FBtype FBcl#dtypeTHIS (www). lt is intrinsically not necessary.

### 1.1.2 FBlock\_FBcl

### ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock/

<u>FBlock\_FBcl.html</u> (www) presents an instance of a Function Block, It refers its <u>FBtype\_FBcl(www</u>) and it has an instance name. The pins of a FBlock instance are then different from the type pins, if multiple pins are existing. Then the type has only one pin which name

### 1.1.3 Pin\_FBcl and PinType\_FBcl

The pins of a <u>FBlock\_FBcl(http://www.v</u> ishia.org/fbg/docuSrcJava\_FBcl/org/vishia/fbcl/f block/FBlock\_FBcl.html) are based on <u>Pin\_FBcl(http://www.vishia.</u> org/fbg/docuSrcJava\_FBcl/org/vishia/fbcl/fblock /Pin\_FBcl.html) with the specificatio ns:

• din:

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock

/Din\_FBcl.html (www):

- dout: <u>./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock</u>

/Dout\_FBcl.html (=>www)

- evin:

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock

/Evin\_FBcl.html

(https://www.vishia.org/fbg/

docuSrcJava\_FBcl/org/vishia/fbcl/fblock/E

vin FBcl.html)

• evout:

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock

/Evout\_FBcl.html

https://www.vishia.org/fbg/

docuSrcJava\_FBcl/org/vishia/fbcl/fblock/E

vout\_FBcl.html)

reference:

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock /PinRef\_FBcl.html (https://www.vishia.org/fb g/docuSrcJava\_FBcl/org/vishia/fbcl/fblock/ PinRef\_FBcl.html)

port: ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock ends with "0999" or "1999", and the instance pins counts from 0 or 1, for example X1..X3 for three inputs. Also not all type pins may be existing for the FBlock, if there are unsused.

The data types of a FBlock can differ from the data types in the type pins, it can be specialized.

/PinPort\_FBcl.html (https://www.vishia.org/f bg/docuSrcJava\_FBcl/org/vishia/fbcl/fblock /PinPort\_FBcl.html)

### 1.1.3.1 PinType\_FBcl

The <u>Pin\_FBcl</u> contains the connection to other pins to other FBlocks whereas the referenced <u>PinType\_FBcl(\_www)</u> contains common information to any pins of instances. It is the base / super class for all pin types. It contains:

- **fbt**: The FBtype where the pin is member of.

- namePin:

https://vishia.org/fbg/docuSrcJava\_FBcl/or g/vishia/fbcl/fblock/DinType\_FBcl.htmltring: It is the pin name same as in the instance or ..1999 or ..0999 for a **multiple pin**.

- **ixPin**: int: The index in the array, and also the bit number in some mask bits.

- kind:

<u>./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock</u> /PinKind\_FBcl.html (https://www.vishia.org/f bg/docuSrcJava\_FBcl/org/vishia/fbcl/fblock /PinKind\_FBcl.html): an enum describes the function.

• mAssocEvData: long: up to 64 event or data associations. This is in IEC61499 the designation

EVENT\_INPUT step WITH x;

1.1 Data Model data classes

. . . . . .

### VAR\_INPUT

### x : REAL;

- But also the back association, which data uses which event, is stored here. evinPin is associated to dinPin and vice versa, and doutPin to evoutPin.

- mAssocInOut: long: up to 64 input and output associations. This is not immediately shown in IEC61499 but can be determined. See also Error: Reference source not found Error: Reference source not found . For Standard FBlocks the output event depends on the state machine. Any output event which may be occure on an input event because of a state entry is contained in the mask for the input event. For the Standard FBlocks with a simple regular state machine the input and the output events are well associated, it is simple. Due to the event association also the data association are marked.

- For a Composite FBlock consisting of an usual graphical interconnection of FBlocks the input – output -association are an result of the connections.

- Note that detail informations about event and data input output mapping are contained in the EccAction\_FBcl to the states. This informations are used for evaluation of the inner content of a module.

- The <u>fblock/DinoutType\_FBcl</u> (www) contains also a data type information for the dinPin and doutPin as well as also for

refPin and portPin:, see Error: Reference source not found Error: Reference source not found

The <u>EvinoutType FBcl(www</u>) contains te association between prepare and update event as number assocEvPrepUpd related to the ixPin, see <u>Error: Reference source</u> not found Error: Reference source not found

• The

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock /EvinoutType\_FBcl.html(https:// www.vishia.o rg/fbg/docuSrcJava\_FBcl/org/vishia/fbcl/fbl ock/DinoutType\_FBcl.html) contains also references to ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock /EccAction\_FBcl.html(https://vishia.org /fbg/docuSrcJava\_FBcl/org/vishia/fbcl/fblo ck/DinoutType\_FBcl.html) for immediately execution of actions to events, see also

• The

./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock

/PinTypeRef\_FBcl.html(https://

www.vishia.or

g/fbg/docuSrcJava\_FBcl/org/vishia/fbcl/fbl

ock/PinTypeRef\_FBcl.html) refers with

FBtype\_FBc1 fbRef the type of the

reference.

## 1.1.3.2 Association between Event and Data Pins

The Pins in FBlock\_Type\_FBcl are contained in adequate arrays. The position in the arrays are used for bit masks mAssociatedInOut and

PinType\_FBcl#mAssociatedEvData www.

### 1.1.3.3 Associaton between Input and Output pins

This should be contained in EccAction\_FBcl

### 1.1.3.4 Association between prepare and update events

Theelementcontains the index of the prepare event in aEvinoutType\_FBcl#assocEvPrepUpd(www).given update event.

### 1.1.3.5 Multiple pins

A multiple pin is pin definition in a PinType\_FBcl which can be represented by more as one pin on the FBlock\_FBcl instance. This is typically used for expressions, adders or such. In IEC61131 and also IEC61499 this is not intended because the implementation languages cannot deal with it. But this idea is similar "variable number of arguments" in programming languages such as C or Java.

For input via FBUMLgI it is desired and for code generation from FBcI this is not a problem. There is a tricky possibility to store a pin in the FBtype\_FBcI which presents multiple inputs:

The name of the pin should end with ...0999 or ...1999, for example "X1999".

1.1.3.6 Operations or Actions assigned to the Pins, code generation

The **EvinType\_FBc1** has usual an assigned **Ecc\_Action\_FBc1**. On inner Pins of a module the input event is related to a pin of type Evout\_FBcl, and also a data inputs are offered with a Dout\_FBcl, an output to the inner FBlocks of the module, the actions are assigned to the common class PinType\_FBcl. TODO it's better it is dedica ted.

The **DoutType\_FBc1** has an assigned **Ecc\_Action\_FBc1** if the inner logic of a **FBtype\_FBc1** comes from a **Composite FBlock** (a FBlock with graphical content). Then this action describes the access operation to this output pin or also to more as one related output pins, depending on code generation rules.

For **Standard FBlocks** the outputs are immediately the output variables which are set

The "999" suggests "many". The number should not be necessary as normal pin Name.

If the FBtype\_FBcl has such a pin, any pin number from ...0 or just ...1 is available and refers the same pin "...0999" in the type. The pins has all the same properties, but of course different data connections, or different constants, or also different data types just as pins of instances have in comparison to the type pins. The code generation can deal with this situation.

If such an design should be implemented in original IEC61499 environment (for example fortis), a proper type should be present. Or just, fortis can also be enhanced to deal with this situation.

by the actions on the **EvinType\_FBc1**, or depending on the code generation, they are simple access operations ("*getter*").

**Simple FBlocks** has only one Action which may be stateless. If it is stateless then it is an expression. For that the **EvoutType\_FBc1** has assigned an **Ecc\_Action\_FBc1** which calculates the expression tracked backward. The action or just **operation** of a stateless Simple FBlock with one output can be written in an expression line.

If a *Simple FBlock* (also an expression) has more as one output, the outputs are presented by inner variables. It means the calculation of such an expression is broken.

### **1.1.4 Write instances for FBlock\_FBcl, FBtype\_Fbcl, Module\_FBcl**

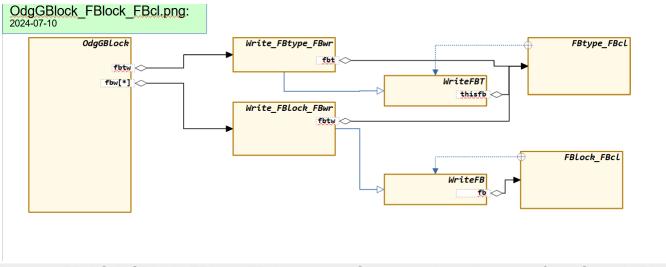

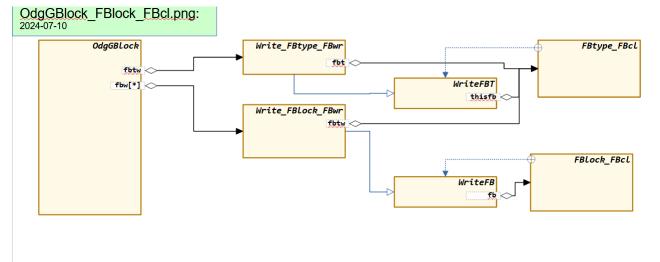

Figure 2: FBcl/OdgGBlock\_FBlock\_FBcl\_omd.png Overview class diagramm form Graphic Block to FBlock\_FBcl

This image shows the writing access to **FBlock\_FBc1** or **FBtype\_FBc1** via Writing wrappers, here from an Graphic blocks (GBlock) as read from the odg-graphic.

A box in the graphic presents a so named GBlock (graphic block), which is one of the graphic presentation of a FBlock\_FBc1 or a FBtype\_FBc1 . But a FBlock\_FBc1 or FBtype\_FBc1 can be presented with more as one GBlock. That's why it is important to associated the OdgGBlock in an early step to the appropriate FBlock\_FBc1 and its FBtype\_FBc1 or only to its FBtype\_FBc1 if a class (type) is presented. But this FBcl blocks are accessed via the org.vishia.fbcl.fblockwr.Write\_FBlock\_FBwr

(www) .and Write\_FBtype\_FBwr (www). This is a pattern to prevent writing (creating) operations in the FBlock\_FBcl and FBtype\_FBcl class, which is usual used in hence normally offered only for read only usage. The write operations with access also to private data of FBlock\_FBc1 and FBtype\_FBc1 is done with an inner class in FBlock\_FBc1 and FBtype\_FBc1 WriteFB and WriteFBT, which can also access private elements. This inner class is now the super class of the Write\_FBlock\_FBwr and Write\_FBtype\_FBwr . Hence the inner changing operations for FBlock\_FBc1 and FBtype\_FBc1 are reached via protected access. With this pattern no public changing operations are able to reach outside of this wrapping classes Write\_FBlock\_FBwr and Write\_FBtype\_FBwr.

But after all XML data are gathered, on end of <u>gatherGraphic(xOdg)</u> (www), neither the Write\_FBlock\_FBwr and Write\_FBtype\_FBwr nor the FBlock\_FBc1 and FBtype\_FBc1 are filled with data. The data are only contained in OdgModule and its OdgGBlock and OdgGPin instances due to the graphic.

### 1.1.5 FBexpr\_FBcl: FBlock for expressions, presentation in FBlock\_FBcl

#### Figure 3: FBcl/FBexpr\_omd.png class diagramm presentation of FBexpr with FBlock

An <u>FBexpr\_FBcl</u> (www) is generally also a FBlock. The difference is: The Code generation does not base on a background functionality. The FBtype\_FBcl also referenced from an FBexpr\_FBcl has never a model referred (the aggregation FBtype\_FBc1#md1 is null) nor a able to found existing target language code. The code generation is done exclusively from the information given in the graphic by this both objects and their pin objects.

### **1.1.6 Module with FBlocks**

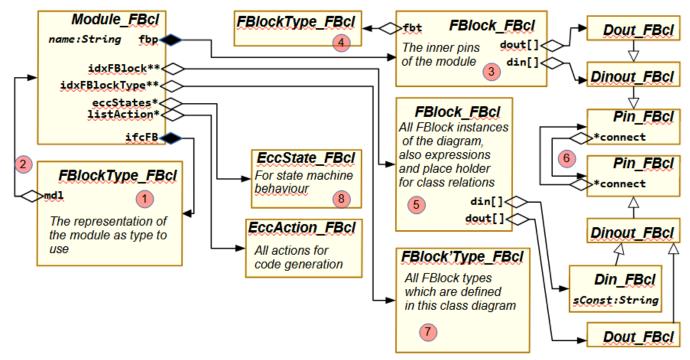

Figure 4: FBcl/Module\_FBcl.png: Module and its inner FBlocks

Some pages in Libre/OpenOffice-draw (or from another input file) builds a ./../docuSrcJava FBcl/org/vishia/fbcl/fblock/Mo dule\_FBcl.html (www). The module can be presented any time as **Composite FBlock type** in IEC61499.

The image shows the important ones:

- (1) The representation of the module to outside with th е ./../docuSrcJava FBcl/org/vishia/fbcl/fblock /FBlockType FBcl.html( https://vishia.org/fbg/docuSrcJava FBcl/or g/vishia/fbcl/fblock/FBlockType FBcl.html) is referenced as ifcFB(interface FBlock), and is referenced as mdl from there (2). This back reference can be removed if the module is code generated and the inner data are no more necessary. The interface FBtype FBcl remains then library as module.

- (3) The pins of the module to outer counterpart to the pins in the ifcFB) are

contained in the referenced FBlock via fbp (FBlock for pins). Whereby the input pins are here output pins to the inner wiring inside the module and vice versa. The aggregated FBtype\_Fbcl (4) is only internally necessary, it is also mirrored in respect to the pin direction to (1).

- (5) The module consists of many FBlocks, which are referenced all sorted by name via idxFBlock. Also expressions are FBlocks

- (6) Right side it is shown that these FBlocks are wired together with its pins, and also wired to the module's I/O-pins.

- (7) Only that FBtype\_FBc1 are indexed via idxBlockType which are defined in this module. Used FBtype\_FBc1 from FBlocks as given are not contained in this index.

- (8) Also States and actions are referenced, see chapter TODO

### 1.1.7 DType\_FBcl and DTypeBase\_FBcl

### 1.1.7.1 Using DType\_FBcl

Instances of ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock/Dat aType\_FBcl.html (www) are referenced from data pins, see chapter <:@ref:#173:8.1.3 Pin\_FBcl and PinType\_FBcl.>. They contains

- dt: The reference to the basic data typ e: ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock

/DataTypeBase\_FBcl.html(http:// www.vishia.o rg/fbg/docuSrcJava\_FBcl/org/vishia/fbcl/fbl ock/DataTypeBase\_FBcl.html)

- sizeArray:

- 0 for scalar,

- 1.. for a one dimensional array.

- -1 arrayUndef not yet defined

- -2 arrayFree Array with a variable size but given on runtime

- -3 arrayList A container as list

- -4 arrayKeyList A container as sorted list.

The same instance of **DType FBc1** is often used by several pins of the same FBtype FBcl or FBlock FBcl and also shared between some or many pins inside a module, whenever the same data type is used. Generally connected pins refer the same instance of DType FBc1 on both ends. For а ./../docuSrcJava FBcl/org/vishia/fbcl/fblock/Mo dule FBcl.html (www) and also inside ./../docuSrcJava FBcl/org/vishia/fbcl/fblock/FBI ock FBcl.html (<u>www</u>) and ./../docuSrcJava\_FBcl/org/vishia/fbcl/fblock/FBI ockType FBcl.html (www) there is a container dtypes, which refers all non full specified DType FBclinstances used in the pins of the FBlocks. Changing this only few instances of Dtype\_Fbc1 can manipulate all data types using it. For example a module can code generated as scalar functionality or alternatively as vector, or for float arithmetic, and alternatively for double or integ er.

There are a few "fixed" Dtype\_Fbc1 instances. That are these which refers the basic types without array or container designations. Often this instances are used, and then it is the same in the pins of FBtype\_FBc1 and Fblock\_Fbc1.

Instances of DType FBc1 which are not full dedicated in a used FBtype FBclare never copied to the FBlock FBcl, because they should be adapted (changed). That is especially if the DTypeBase FBc1 is a non full specified data type such as "ANY NUM" instead float, int etc. That is typical for some expressions or mathematically operations. This is done first by creating a clone of the DType\_FBc1 instance for the pins of a FBlock FBcl from the pins of the FBtype FBcl. The clone is necessary because afterwards the DType\_FBc1 can be changed, independent of the DType FBc1 instances in the FBtype FBc1. This changes are done to get more deterministic types. Either the dt reference in a DType FBc1 can be changed, or by replacing the instance of DType FBc1 in all appropriate pins.

But while forward and backward propagation the number of different instances of DType\_FBc1 is reduced.

For the last action all **DType\_FBc1** instances contains a reference:

- usingPins: Reference to all pins using this type. It is null (not existing) if all DType\_FBc1 refers a deterministic type. This reference is used to change a changed DType\_FBc1 on one pin in all other appropriate pins.

- deps: This container references all DType\_FBc1 which are not the same but depending in some characteristic. If for example one DType\_FBc1 is complex, another is real, or one is scalar and the other is an array, but both should have the same numeric type. then changing the

type in the one **DType\_FBc1** should be done also in all depending **DType\_FBc1** instances.

### 1.1.7.2 Using DTypeBase\_FBcl

All types in <u>fblock/DataTypeBase\_FBcl((www)</u>) are designated by a <u>public final char</u> typeChar. One char is enough and concisely

The basic types without container and array specifications are either standard types, contained in DTypeBase\_Fbc1.stdTypes.

Or they are the reference type to used FBtype\_FBc1. In IEC61499 these are "ANY\_DERIVED" types, applied to "TYPE END" language constructs. In the UFBgl these should be able to map to specific FBtype\_FBc1. The DTypeBase\_FBc1 contains a field typeRef for this reference. The DTypeBase\_FBc1 instance for a specific FBtype\_FBc1.reference is always created for the FBtype\_FBc1 itself referenced their with dtypeTHIS.

### 1.1.8 Event tree node

The event connections in a module builds firstly a tree of event nodes. But this tree is also characteristics by some cross event connections.

For code generation the tree of event nodes is determining the order of execution. Primary the order of execution is only the event flow. But this is too detailed, not able to overview. Also the algorithm of roll out the event flow is not very obviously.

That's why after build all event connections a tree of event node is built. This tree structure has an **Iterator** which offers the member of this event tree node in a defined order which is used also for code generation as also in the event connection part of the fbd file (IEC61499). But for the cross connections in the event flow there are some special cases.

Look on the following example:

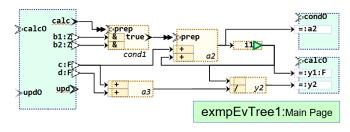

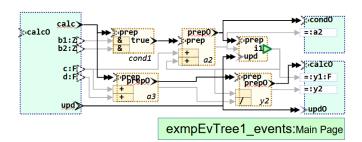

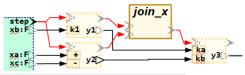

#### Figure 5: odg/exmpEvTree1.png

The image shows a simple expression relation, but with a boolean event expression: The FBexpr a2 and follow does only act if the expression evaluates to true. But this is not primary important for the following considerations, only for code generation.

The shown data connections and the drawn event connection results in the following event flow, see **1.6.2** Identification of the event flow due to data flow page **40**:

Figure 6: odg/exmpEvTree1\_events.png

The data connections are shown in gray.

The fbd output file (IEC61499) shows the following event connections:

EVENT\_CONNECTIONS calc TO a3.prep a3.prepO TO y2.prep y2.prepO TO calcO calc TO cond1.prep cond1.true TO a2.prep a2.prepO TO condO a2.prepO TO i1\_X.prep i1\_X.prepO TO i1.prep upd TO i1.upd upd TO updO END\_CONNECTIONS

The indentation allows detect the tree structure of the event connection. Sorting of connections are always alphabetically, hence first a3.prep is shown. The event connection chain continues with y2.prep in this line till calco. The second connection from calc goes to cond1.prep, continues with its true event output, forces cond0, and also the preparation of the state variable i1, which is updated with i1.upd.

This is also exact the order of generated code.

How the event connections are sorted? Using an <u>fblock.EvoutTreeNode\_FBcl</u> (www):

The next image right side shows the complete instance view of the OFB module in the images *Figure 5: odg/exmpEvTree1.png* and *Figure 6: odg/exmpEvTree1\_events.png*.

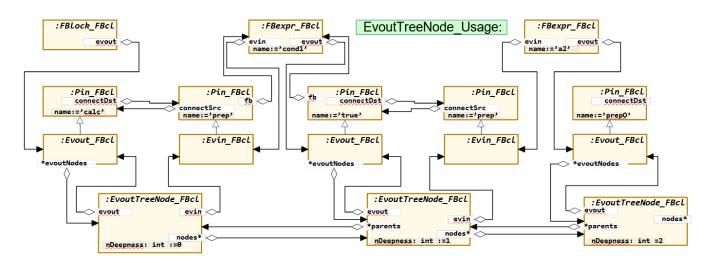

Figure 7: FBcl/EvoutTreeNode\_Usage.png

The image shows as class/instance diagram the first two event connections of **Figure 5**: **odg/exmpEvTree1.png** from **calc** to the FBexpr **cond1** and then from its output **true** to the next **a2.prep**.

The information for connecting events are repeated here. The connection is a property of the pins already, and twice given by designation of the evout - evin pair in the <u>fblock.EvoutTreeNode FBcl</u> (www). Also the

relation between evin and evout of the same FBlock\_FBc1 can be traced by the operation fblock.Evin\_FBcl#iterCorrespondEvout(...) (www). Just this is done to built this event tree.

The intrinsic information is just the order of event connections which is also the order of execution in the code generation, see **1.7.2** *Tracking the event chain for a module's operation* page **52**. This gets important also for Join of events:

### 1.2 Reading graphic files from different inputs, UFBglConv

The <u>org.vishia.fbcl.UFBglConv</u> (www) is the main class to convert several input files, and outputs IEC61499 files and code generation for the target system.

This class has a main(String[] args) entry to invoke with java command line. Additional

- <u>UFBglConv#smain(...)</u> (www) and

- <u>UFBglConv#amain(CmdArgs...)</u> (www)

are given to call it from a Java application inside, and to call it from a JztxtCmd script.

### **1.2.1 Complete a module**

Completion of a module is done whenever the module is read completely, before the next module is read. The operation Write\_Module\_Fbwr#completeMdl(). does the following actions:

- completeMissingEventPinsInTypes():

- postPrepareFBlocks()

- postPrepareDtypesToIfc

- completeFBoper() for all listFBoper

• propgDtypes(...): This is the essential operation to equalize the used Dtype\_Fbcl instances via all connections and depending pins. Non full determined data types in a FBtype will be determined for the FBlock instances due its connections.

• Dataflow2Eventchain\_Fbrd#prc(): This is the essential operation to create the correct execution order of all internal operations of the module, described by the event flow. The event flow follows the data flow. See chapter TODO

• **completeAllFBlockTypePinsInModule()**: All FBtype should have the pins, adequate read library modules.

After parsing the commands **execute(...)** is called. This operation does the following:

• First, all input files in CmdArgs#listFileIn from the cmdline arg -i:path/to/input.file were processed, the type (extension) of the input file determines the reading conversion. odg-files are read, see chapter.

• The data of this first step are stored in the Write... instances of TODO

• all parsed modules are stored in Prj\_FBCLrd#idxWriteModules.

Whereby the type of the conv

• **completeAllMdlPins(null)**: establishes the pins for the FBtype of the module

• createAllMdlIfcPins(): The FBtype\_FBc1 instance for the module's interface is the mirror of the internal Module\_FBc1#fbp pin - FBlock and its associated FBtype\_FBc1. The last ones are created with gathering the pins of the module in the module's implementation graphic. The pins are mirrored because for example an evin of the module seen from outside is used internally in the module as evout as source for the internal wiring.

This operation builds the pins for the module's interface FBtype\_FBc1 instance from the given internal pins of the module. For an existing EvoutType\_FBc1 as input of the module or output for internal using a EvinType\_FBc1 with the same name is created, etc.

- setExprOperatorToPins();

- adjustFBexrFnDtypes():

### 1.2 Reading graphic files from different inputs, UFBglConv

### 1.3 Read data from LibreOffice odg files

### **Table of Contents**

20

| 1.3 Read data from LibreOffice odg files                          |  |

|-------------------------------------------------------------------|--|

| 1.3.1 The file format of odg – content.xml                        |  |

| 1.3.2 Read content.xml from the odg graphic file to internal data |  |

| 1.3.3 Sorting XML data to Shapes for each page                    |  |

| 1.3.3.1 Gather Pages and the title                                |  |

| 1.3.3.2 Gather all shapes per page                                |  |

| 1.3.3.3 Evaluate the shapes                                       |  |

| 1.3.3.4 Evaluating Pin texts                                      |  |

| 1.3.4 Gather data for OdgModule page by page                      |  |

| 1.3.4.1 Associate the page to a module                            |  |

| 1.3.4.2 Aggregation to FBcl blocks via Writer                     |  |

| 1.3.5 Build the data in FBcl data                                 |  |

| 1.3.6 Connect all FBcl pins due to connection of graphic pins     |  |

| 1.3.7 Preparation of Expressions from odg                         |  |

| 1.3.7.1 createExprPins() createExprPins()                         |  |

| 1.3.7.2 createExprPinAndKpin                                      |  |

|                                                                   |  |

### 1.3.1 The file format of odg – content.xml

| q:\vishia\SwEng\doc\ofb-Template.otg.zip\*.* |     |             |         |  |

|----------------------------------------------|-----|-------------|---------|--|

| Name                                         | Ext | Size        | +Date   |  |

| <b>雀</b> []                                  |     | <dir></dir> | 2023-04 |  |

| [Configurations2]                            |     | <dir></dir> | 2023-04 |  |

| [META-INF]                                   |     | <dir></dir> | 2023-04 |  |

| [Thumbnails]                                 |     | <dir></dir> | 2023-04 |  |

| 🔮 content                                    | xml | 59.824      | 2023-04 |  |

| 🔮 meta                                       | xml | 1.272       | 2023-04 |  |

| 🗋 mimetype                                   |     | 52          | 2023-04 |  |

| settings                                     | xml | 17.802      | 2023-04 |  |

| 🔮 styles                                     | xml | 59.184      | 2023-0  |  |

|                                              |     |             |         |  |

#### Figure 8: OFB/ContentOfodg.zip.png

Let's have first a look to the file format from Libre Office. The odg format is a zip archive. You can add the extension zip, and then look into with a zip utility.

Right side you see a screen shot from the opened zip file (with Total Commander). The zip file contains three important xml files.

- content.xml contains the graphic itself

- styles.xml contains the style sheet settings. If you want to copy your settings between some files, you can copy this styles.xml inside the two zip file. It seems to be safe.

- settings.xml is not relevant for the content itself, also the other files are helper for the Office tool.

Now have a look inside the content.xml (pressing F3 in Total Commander to view to pure textual content:

It is one very long line without structure not well human readable, but it is well formed XML.

| <b>2</b> 1                      | .ister -                                  | [T:\TEMP\                                                | _tc\content.                        | xml]                                                | —                                                                                                                                                                                                                                                                                                                                               |                              | ×                      |

|---------------------------------|-------------------------------------------|----------------------------------------------------------|-------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|

| File                            | Edit                                      | Options                                                  | Encoding                            | Help                                                |                                                                                                                                                                                                                                                                                                                                                 | 7                            | 4 %                    |

| Kof<br>xml<br>xml<br>sty<br>stu | fice:<br>ns:of<br>ns:pr<br>le:fo<br>le:fo | document<br>="urn:oa<br>esentati<br>nt-famil<br>nt-famil | sis:names<br>on="urn:o<br>y-generic | xmĺns:o<br>:tc:ope<br>asis:na<br>="swiss<br>="moder | ffice="urn:oasis:names:tc:opendocument:xm<br>ndocument:xmlns:of:1.2" xmlns:xforms="htt<br>mes:tc:opendocument:xmlns:presentation:1.<br>" style:font-pitch="variable"/> <style:fon<br>n"_stule:font-nitch="fixed"/&gt;<stule:font-< th=""><th>p://www<br/>0" xmlı<br/>t-face</th><th>w.w3.<br/>ns:sm<br/>styl</th></stule:font-<></style:fon<br> | p://www<br>0" xmlı<br>t-face | w.w3.<br>ns:sm<br>styl |

But there is an option in LibreOffice: Menu "Tools -> Options", Select "LibreOffice -> Advanced". press Button [Open Expert *Configuration*], then search "*PrettyPrinting*" or configuration select the tree in "org.openoffice.Office.Common -> Save -> Document", select the property "PrettyPrinting" and set it to true. See also https://wiki.documentfoundation.org/Document ation/ODF Markup/en#Pretty Printing

Then the content.xml will be stored with some more lines. It is able to overview. But regard, a newline inside a <text:p> may create at least one space. Hence the <text:p> till </text:p> is still written in a long line (but not too long).

After beautification it looks like (as textual snippet):

This is right side truncated, it shows the graphical "group" with the "ClassA name1" as shown in page . You can see here also the aggregation aggrCX. The style names are not written immediately plain here, instead a

referencing is done, the draw:style-name="gr23" describes some possible direct formatting properties and the references to the knwon style "ofpAggrRight" as you see in the content.xml in the <style...> part.

```

<style:style style:name="gr23" style:family="graphic" style:parent-style-name="ofpAggrRight">

<style:graphic-properties draw:marker-start-width="0.24cm" draw:marker-end-width="0.24cm" f

<style:paragraph-properties style:writing-mode="lr-tb"/>

</style:style>

```

This is all understandable and comprehensible. Hence read out of data is only a problem of sorting.

### 1.3.2 Read content.xml from the odg graphic file to internal data

The <u>org.vishia.xmlReader.XmlJzReader</u> (www) contained in the <u>vishiaBase.jar</u> is used to read the XML data. This class can select determined parts from the XML file, read not all. Therefore a configuration file is used. The data are stored in a common or a specific data class. A possible common class is <u>org.vishia.</u> <u>xmlReader.XmlDataNode</u> (www). But this class is not used here (it is used for the LibreOffice to VML converter).

Instead a specific destination class for the XML data was created: <u>org.vishia.fbcl.readOdg.xml.</u> XmlForOdg (www). The given instance of this class is filled from the XmlJzReader by reading the content.xml. The data are organized proper to the internal XML tree structure. Reading the content.xml is controlled by the config file fbcl/readOdg/xml/odgxmlcfg.xml (www) as part of the jar file vishiaUFBgl.jar.

presents the access to the read XML data. This class was automatically created by calling the tool suite on .../RWTrans/XmIJzReader.html (www) but adapted afterwards. The base class which should not adapted be is readOdg.xml.XmlForOdg Base (www). this class contains the data read from XML. The data structure in this class follows the structure of the fbcl.readOdg.xml.odgxmlcfg.xml (www) which controls interpreting of the XML data. The class to read the XML file is org.vishia.xmlReader.XmlJzReader (www) in vishiaBase.jar file. lt is called the in fbcl.readOdg.xml.XmlForOdg Base (www).

The following code snippet shows how the XmlJzReader is invoked:

```

/**Reads completely the content.xml from the

```

```

* and stores the data in the returned ins...

```

```

* @param fInOdg The file to read

```

```

* @return the read data from XML

```

```

* @throws IOException On file read problems

```

The following text is a data snippet, gotten from the Variable View in Eclipse. odg is the returned instance. The text after a name is the **toString()** output, which contains sometimes only TODO (not used till now) but you can for example see the content of a draw\_page, and hence the XML structure. - It is only an illustration.

```

xOdg: XmlForOdg @unknown:0 XmlForOdg 251 1

idxStyle: Map<String, String> null null

office document content: XmlForOdg$Office d

office automatic styles: XmlForOdg$Office

office body: XmlForOdg$Office body TODO to

office_drawing: XmlForOdg$Office_drawing

draw_page: List<Draw_page> [TODO toStrin

[0]: Object TODO toString XmlForOdg$Dra

draw connector: List<Draw connector> [

draw custom shape: List<Draw custom sh

draw_frame: List<Draw_frame> null null

draw_g: List<Draw_g> [(9.5cm, 4.1cm) +

draw_master_page_name: String Default

draw_name: String page1 String 287 165

draw polygon: List<Draw polygon> [4.2c

draw polyline: <unknown type> null nul

draw_style_name: String dp1 String 289

[1]: Object TODO toString XmlForOdg$Dra

[2]: Object TODO toString XmlForOdg$Dra

[3]: Object TODO toString XmlForOdg$Dra

office font face decls: XmlForOdg$Office f

office_scripts: String null null 16552

office_version: String null null 16552

office_version: String 1.3 String 264 1655

```

As you see, the data structure follows the XML content. The data are mapped from XML to this internally Java data. The mapping depends from the content of the odgxmlcfg.xml file, which controls the XmlJzReader, but this cfg.xml is so completely as necessary.

### 1.3.3 Sorting XML data to Shapes for each page

After reading the XML file the operation <u>OdgReader#gatherGraphic(xOdg)</u> (www) is called. This evaluates the whole XML content, but sorted to pages, because in XML the data are sorted also in page nodes:

### 1.3.3.1 Gather Pages and the title

```

<office:body>

<office:drawing>

<draw:page draw:name="page1" ...

<draw:custom-shape ...

```

For each page, a new OdgPage(nr, xpage, xOdg) is created and first, page.gatherTitleDisabled Area(xpage, xOdg); is called. The title is the box with ofbTitle. It contains the module name for this page and hence it is essential to associate the page to the module. If the module name is commented with leading #, then this page is commented and hence skipped. The module name is essential. Maybe only determined modules are read from XML, controlled by the command line option -im:ModuleName. Pages for each one module should be one after another. If another module starts with a new page, the module is OdgReader#completeModule (www)

The disabled areas in the graphic are important to prevent evaluation of disabled parts.

### 1.3.3.2 Gather all shapes per page

If the page is not skipped, then first all shapes and sorted are gathered by its style information, with its texts and coordinates. This operation. is а formally done by OdgPage#gatherShapes(xpage, xOdg) (www) evaluates It all <draw:custom-shape.... <draw:polygon... and <draw:frame... from the</pre> page, and also *drawig* to evaluate this elements in a group.

From all this elements first the x-y-coordinates are detected. If they are in a range of a disabled area (which is a shape with ofbDisabledArea style), then the shape is ignored. This is the functionality described in html / Handling-OFB\_VishiaDiagrams.pdf: 1.2.1 GBlock styles, ofbpage8andhtml/Handling-OFBVishiaDiagrams.pdf:1.5.1Module in file organized in pagespage19.

Then all other properties of the shape are gathered from XML and stored in instances of <u>OdgShape</u> (www). Any of a shape in the graphic is formally mapped to an <u>OdgShape</u> instance. This can be a pin, a fblock etc. The <u>OdgShape</u> instances are stored sorted to its kind in some lists inside <u>OdgPage</u> (www).

For the shapes the draw style is evaluated (in XML the attribute draw:style-name="..." in the shape). Via the OdgReader#idxFBkindFromStyle (www) and also OdgReader#idxPinkindFromStyle (www) the textual given style name is transferred to the internal used enum.

#### 1.3.3.3 Evaluate the shapes

The approach is, reading all shapes and associating to the internal data of the module due to their graphic style and also due to there relative position. A primary idea for associating pins to blocks was building a group in LibreOffice graphic. But grouping should be seen only as graphic possibility, not for semantic. The position, the pin is inside the shape which represents the block, is the intrinsically possibility of association.

The graphic from **xodg** is evaluated page by page.

As first step in the graphic a shape with the style **ofbTitle** is searched in the page. The textual content till : is the module name. If it starts with **#** the page is disabled (not to evaluate).

Secondly all shapes are evaluated which are block shapes, means they build the frame for blocks. This is checked in gatherFBlockShape(...shape...). This is done first outside and then inside of groups. The graphic styles which build block shapes are ofbFBlock, ofbClass, ofbMldPins and ofbExpression.

After gathering and sorting the shapes there are evaluated. First this is done for the non-pin shapes. Especially first the GBlock shapes with style ofbFBlock, ofbClass, and then ofnNameTypeFBlock and ofnClassTypeName (deprecated). After this operation you have instances of OdgGBlock which referes to FBlock FBcl and FBtype FBcl in your Write Module FBwr. This, first the OdgGBlock are necessary to associate the pins.

The pin shapes which are all stored in OdgPage#shPin are evaluated after detecting alls FBlock shapes. So their OdgGBlock is already stored with its coordinates able to find in ReadOdg.listBlocks\_x and \_y. the operation ReadOdg#searchFbg(...) searches the associated GBlock by coordinates to each evaluated pin. The pin- FBlock association is done with the pin graphic coordinates. At least one rectangle corner point should be inside the rectangle box of the GBlock.

Pins which have not a proper GBlock found can be either a free variable in the module, as ofpVout... or ofpZout..., or also as simple ofPin... with a text designation ...=\$ or ...=& on end. Or an error messages is shown: "Warning ...Pin @...position outside FBlock shape"..

• ofbAccess as style of the found GBlock forces adding the pin with OdgReader#gatherAccessPin(...).

• ofbExpression as style of the found GBlock forces adding via OdgReader#gatherExprPin(...) • All other pins are added via OdgReader#gatherFBlockPin(...) to the found OdgGBlock.

• But pins of style ofpExprPart are sorted as extra shape kind in OdgShape#shExprPart. They are also added to the found GBlock with OdgReader#gatherExprPin(...) without selection of the GBlock kind, but with test of the GBlock kind.

• Pins of style **ofpExprOut** are sorted as extra shape kind in OdgShape#shExprOut. They can be applied either to a GBlock if style ofbExpression or also ofbAccess as their output. Hence, the kind of the found GBlock is tested, and either ... here is a little bit TODO cleanup in sw.

### 1.3.3.4 Evaluating Pin texts

The text inside a pin shape is evaluated on creation of the OdgGPin instance while setting the element OdgGPin#nameType. Then all information from the graphic are contained in a prepared form in the OdgGpin instance, ready to use to later create the adequate Pin\_FBcl instances with the correct derived types.

The Evaluation of the pin texts is done in the constructor of the type OdgNameTypeArray, all which contains semantic relevant information given in the text of the graphic shape for OFB usage. The syntax and meaning explained in html 1 Handlinges OFB VishiaDiagrams.pdf: Texts 1.3 in graphic blocks and pins page 12.

TODO explain short meaning of the info.And how it is parsed.

### 1.3.4 Gather data for OdgModule page by page

The shapes or boxes with style ofbFBlock or also ofbClass are contained in the current odgPage.<u>shFBlock</u> (www). This container is evaluated before the inner shapes of a GBlock as for example odgPage.shPin are evaluated. First a <u>OdgGBlock</u> is created, and then via calling <u>OdgReader.html#assignFBlockName</u> <u>TypeIdCreateFBlock(...)</u> (www) the appropriate FBlock\_FBc1 or FBtype\_FBc1 is searched in the project or it is created. But it is referenced via

#### the Writer classes, see **1.1.4 Write instances** for FBlock\_FBcI, FBtype\_FbcI, Module\_FBcI

### **1.3.4.1** Associate the page to a module

After the Shapes are built for each one page inside the operation <u>OdgReader#</u> <u>gatherGraphic(xOdg)</u> (www), and after first the <u>ofbTitle</u> is scanned, the page is associated to the module, which name is contained in the <u>ofbTitle</u> box.

The module name is searched in <u>OdgReader#idxOdgMdl</u> (www) idxOdgMd1. It is found or new created and stored there as <u>OdgModule</u> (www) OdgModule instance. Each page completes the module internal data. The next image should give an overview over that data:

#### 1.3.4.2 Aggregation to FBcl blocks via Writer

*Figure 10: FBcl/OdgGBlock\_FBlock\_FBcl\_omd.png Overview class diagramm form Graphic Block to FBlock\_FBcl*

This image shows the existing Graphic blocks (GBlock) as read from the odg-graphic and its relationships to the FBcl classes. The FBcl classes are created here, but not completed.

A box in the graphic presents a so named GBlock (graphic block), which is one of the graphic presentation of a FBlock FBcl or a FBtype\_FBc1 . But a FBlock\_FBc1 Or FBtype\_FBc1 can be presented with more as one GBlock. That's why it is important to associated the OdgGBlock in an early step to the appropriate FBlock FBcl and its FBtype FBcl or only to its FBtype FBc1 if a class (type) is presented. But this FBcl blocks are accessed via the org.vishia.fbcl.fblockwr.Write FBlock FBwr (www) .and Write FBtype FBwr (www). This is prevent writing а pattern to (creating) operations in the FBlock\_FBcl and FBtype FBcl class, which is usual used in hence normally offered only for read only usage. The write (empty page)

operations with access also to private data of FBlock\_FBc1 and FBtype\_FBc1 is done with an inner class in FBlock\_FBc1 and FBtype\_FBc1 WriteFB and WriteFBT, which can also access private elements. This inner class is now the super class of the Write\_FBlock\_FBwr and Write\_FBtype\_FBwr . Hence the inner changing operations for FBlock\_FBc1 and FBtype\_FBc1 are reached via protected access. With this pattern no public changing operations are able to reach outside of this wrapping classes Write\_FBlock\_FBwr and Write\_FBtype\_FBwr.

But after all XML data are gathered, on end of <u>gatherGraphic(xOdg)</u> (www), neither the Write\_FBlock\_FBwr and Write\_FBtype\_FBwr nor the FBlock\_FBc1 and FBtype\_FBc1 are filled with data. The data are only contained in OdgModule and its OdgGBlock and OdgGPin instances due to the graphic.

### 1.3.5 Build the data in FBcl data

The data in FBlock\_FBc1 and FBtype\_FBc1 as well as also in Pin\_FBc1 and PinType\_FBc1 and its derived classed and also in Module\_FBc1 are designated as FBcl data. FBcl is the Function Block connection language which is independent of the Libre/OpenOffice odg graphic and the base for the IEC61499 presentation and also for code generation.

The Module\_FBcl and also FBlock\_FBcl, FBtype\_FBcl are created on creation of the Graphic representations OdgGBlock and OdgGPin. But they are not complelely filled.

The completion of the FBcl data from the graphic representation is done in

readOdg.<u>OdgModule#buildFbgData(...)</u> (www). This does the following:

- create all FBlock pins: <u>OdgModule#createFBPins\_duetoGBlockPi</u> <u>ns()</u> (www).

- createFBPins\_duetoGBlockPins()

- createFBclConnectionsFromGraphic()

- buildAssociatedMdlEventDataPins()

- buildAssociatedFBtypeEventDataPins()

- Write\_Module\_FBwr#completeMdl()

### 1.3.6 Connect all FBcl pins due to connection of graphic pins

The graphic connections are done page per page of the odg file after reading the shapes, see **1.3.4 Gather data for OdgModule page by page** page **24**. The graphic connections are not the same as the real FBcl connections:

• The graphic connections are oriented general to one graphic page. But the graphic of one module can use more as one page. Connections over pages are done by

- Xref Cross references

- Using free variables

• Use the same FBlock instance (or Type) more as one time with another Graphic GBlock.

It means, after gathering the graphic, on finishing reading one module, the graphic connections should be translated to FBcl connections in the module without the graphic page orientation.

That is done for all graphic pins

- (readOdg.OdgGPin) in all graphic

- readOdg.OdgGBlock of the current

- readOdg.OdgModule.

For that the operation <u>OdgModule#createFBcl</u> <u>ConnectionsFromGraphic(...)</u> (www) is called. This gets GBlocks from:

- OdgModule#idxModuleIfc (www): All module pins

- <u>OdgModule#idxGBlock</u> (www): All GBlocks of the module

- OdgModule#idxGExprByName (www): All expression pins

- <u>OdgModule#idxGAccessByName</u> (<u>www</u>): All Access FBlock pins

From the graphic connection first a textual connection is searched. That is the denomination of <code>@fb@pin...=:</code> in the pin

description. The named FBlock\_FBcl and its pin is searched and connected.

Furthermore, all outgoing connections are tracked. This is not bound to output pins, all pins are evaluated. Because an outgoing connection can also start from an input pin, which is connected to any output.

For tracking output the operation <u>OdgModule#</u> processFBlockPinGraphicConnection(...)

(www) is called. It calls after a short preparation (create necessary pins which are only given in the type) the operation OdgModule#connectViaDemuxXref(...) (www). This operaton is recursively called inside if the connection has more paths.

For the graphic connection it should be regarded:

Using Xref: Then the graphic connection goes to any Xref GBlock. There are more as one Xref GBlocks with the same Label, especially on several pages. All this GBlocks with the same label references to only one readOdg.OdgXrefGraphic which is derived from readOdg.OdgGBllock. It means any Xref graphic appereance does not have its own OdgGBlock, it has a common one valid for the whole OdgModule. It is referenced sorted by name the container in odgReader.OdgModule#idxXrefGrpahicBy Name (www). But for the connection this is not important. Important is the fact. That all incomming connections (usual one, onle source) contained the one is in OdgGBlock#fbPinDst, and all outgoing connections from are staring OdgGBlock#fbPinSrc. With that. а connection via Xref can simple tracked by regarding all outgoing connections if the incoming connection hits the Xref.

• Using Demux FBlocks. They have the graphic style **OfbDemux**, respectively the pins have **ofpDemux**.

The Demux FBlocks are a little bit more complicated, hence explained following:

If a graphic connection from any source pin ends on a odpDemux pin, then this Demux pin contains a selection String, named in the software as pinDemuxSe1.

Writing with or without [...] does not play a role, the string inside the [...] is used or the given string without leading and trailing spaces. Then the connection is continued with the mulitplex pin, which is in OdgGBlock#fbPinSrc of this Demux Gblock. But the selection String named pinDemuxSel in the Java source is transported as argument of OdgModule#connectViaDemuxXref(...) (www)

\*\t

### 1.3.7 Preparation of Expressions from odg

See also the data description of FBexpr in chapter **1.1.5** FBexpr\_FBcI: FBlock for expressions, presentation in FBlock\_FBcI page **12**

1.3.7.1 createExprPins(...) createExprPins(...)

In createExprPin(...) (www?) all pins from a OdgFBlockGraphicInstance are evaluated. This are the drawn pins in the graphic, type is OdgPinInstance (www?). The kind of the pin due to the graphic style is stored in ...

First the kind of all pins is checked, to check which FBtype\_FBcl of the FBexpr should be taken. The kind depends

• how...

An internal String array **sExpr[3]** accumulates the information about the operators of all pins. It is created empty first. The content contains elements, separated by comma , which are stored in this form as constant value for the **expr** input of the FBexpr seen in the FBcl file (IEC61499).

- The **sExpr[0]** holds the operators of the Din pins.

- · Whereby the first element contains in two characters the access type of the FBexpr and the basic operation. The access type is -& = for an inline expression (without data output), as an inline expression but with one or some outputs beside (possible only if an textual given operation is given) and an expression which as a variable on its output, hence called as statement to set it. This last variant can also have some outputs beside (more outputs, all have variables associated). The same is for a % \$, in this order, but with the property that the expression has a THIS aggregation to its FBlock, it is a FBoper, see html / Handling-

The internal Handling of expressions needs a little bit explanation. Refer to chapter <u>html</u> / <u>Handling-OFB\_VishiaDiagrams.pdf</u>: **1.7** *Expressions inside the data flow* page to see the capabilities of expressions.

#### <u>OFB\_VishiaDiagrams.pdf</u>: **1.7.9** *FBoper, operation for a FBlock* page **47**

- The basic operation on sExpr[0].charAt(1) is

\* & v ^ = h for the operation types ADD, MULT, AND, OR, XOR, CMP and SHIFT. For all Din pins the operator should be given. The graphic may omit the operator if it is the default operator for the operation. But here it needs to be specified anyway.

- Also an unary operator is written here, at end of the element. Unary operator are only - ~ /, last for reciprocal.

- The sExpr[1] holds the operator for the operators of the K pin. The first element is empty, the sExpr[1] starts with ",...". Not existing K pins are presented with an empty element. It means sExpr[1]=",,\*" if only the K2 exists. The K1 position is empty. The K operator should be given anyway, also it is omitted in graphic for the default, often /.

XXXX

For this image the sExpr[0] contains "=\*,\*,/" because first char = means, it is an assignment to a variable. The next \* determines it as a MULT expression. Then the input operators follow with ,\*,/" for \* and /. The sExpr[1] contains ",/," because the K1 is used with division, and the K2 is not existing. For all pins **createExprPinAndKpin** is called. This completes the **sExpr[]** succesive for each pin.

At least, if all pins are created, the String for sExpr[0] is adjusted. All din pins should have its correct operator, But in the graphic the default operator can be omitted. It means it should be completed. Note that on code generation, the operator on the first pin may be remove again in an expression, for example +a +b is translated to (a+b). This is done in code generation. Here the operators are completed. For all CMP operation = is written as default, not ==, for the Din pin which is compared to. = is the default operator for the input to compare. Note that in opposite, in IEC61499 as also in IEC61131 the compare operator for 'equal' is =, and not == as in C/++, Java and other programming languages. Whereas for an

### 1.3.7.2 createExprPinAndKpin

In **createExprPinAndKpin(...)** for one gpin OdgGpin (www?) the appropriate . This are the drawn pins in the graphic, type is OdgPinInstance (www?). The kind of the pin due to the graphic style is stored in ...

(emptyline)

assignment := is used instead = in current familiar languages. That was the writing style also in the first structured language Algol, as also in Pascal, which were present in the time of foundation of the IEC61131 automation programming language (1980th. In opposite, the founder for the C language have introduced the shorter = for the assignment, but then used == for the equal operator. This contradiction still reaches us here today.

createDoutExpr(...) handles all pins with style ofpDout, ofpVout, ofpZout, ofpExprOut. The first name of one of these pins but not a ofpExprOut determines the name of the FBexpr instance.

The syntax of an ofpExpPart ist evaluated in OdgModule#checkPrepareExprOperator(...) (www)

Tip for debug: first lines there, the complete text from graphic can be tested, to set a debug.stop

### 1.4 Read data from Simulink

TODO

### **1.5 Read data from IEC61499 text files (fbd)**

TODO

### **1.6 Complete Preparation of the module**

### **Table of Contents**

36

| 6 Complete Preparation of the module                                                  |    |

|---------------------------------------------------------------------------------------|----|

| 1.6.1 Forward and backward propagation of data types                                  | 37 |

| 1.6.1.1 Forward/backward propagation of dedicated pins                                |    |

| 1.6.1.2 Forward and backward propagation of non dedicated pins                        |    |

| 1.6.1.3 Forward declaration for depending pins of a FBtype                            |    |

| 1.6.2 Identification of the event flow due to data flow                               |    |

| 1.6.2.1 UFBgI: Binding event to data on in/outputs                                    |    |

| 1.6.2.2 Resulting evout because of evin of a FBlock                                   | 40 |

| 1.6.2.3 Some Contemplation to bind data to events, event cluster                      | 40 |

| 1.6.2.4 Info in pins for data to event processing                                     |    |

| 1.6.3 OFB: Build the event chain                                                      |    |

| 1.6.3.1 Start on module's evin                                                        |    |

| 1.6.3.2 propagate one step forward                                                    |    |

| 1.6.3.3 Check all other dinDst, build listEvoutSrc                                    |    |

| 1.6.3.4 Discard the step if not all doutSrcOther are driven by events yet             |    |

| 1.6.3.5 Connect the events if all dinDstOther are driven by events using listEvoutSrc |    |

| 1.6.3.6 Put evoutDst in the queue to continue                                         |    |

| 1.6.4 Completion of condition events                                                  |    |

### **1.6.1** Forward and backward propagation of data types

This is a topic of the data flow. The forward declaration is done by the operation

fbcl.fblockwr.Write Module FBwr#

propgDtypes(log) (www)

#### **1.6.1.1** Forward/backward propagation of dedicated pins

The data type propagation starts by adding all dout pins of all FBlocks and dedicated pins of the *module's inputs* which are formally an Dout\_FBc1 (to the inner of the module) which have a dedicated <u>fbcl/fblock/DType\_FBcl</u> (www) to an internal List<Dout\_FBc1> listDout.

From this pins the connection is traced to connection **Din\_FBc1** pins to following FBlocks, which then have the same data type. This is set, or checked. Conflicting data types are reported.

Then, in the reached FBlock\_FBc1, depending pins which are yet not full dedicated are set, see next sub chapter. The dout pins, which are yet dedicated, are added to the List<Dout\_FBc1> listDout to use on further forward propagation

Also from begin, a HashMap<Din\_Fbc1, Din\_FBc1> idxDinBackward is filled with all outputs of the module which are Din\_FBc1 din pins, which are dedicated. This HashMap is filled also with all found din pins of all FBlocks which are now propagated, because of backward propagation if necessary. This HashMap idxDinBackward is also used to check whether a pin reached on forward propagation is already propagated, hence by another forward propagation and the related propagation inside the FBlock. If it is so, only the data type is tested whether it is matching. The propagation stops here.

After all forward propagation are done, all remaining Din\_FBc1 din pins in the HashMap<> idxDinBackward are handled for a backward propagation. This din are either full dedicated from beginning, or they are dedicated now because of the forward propagation, and are **not reached** by the forward propagation (because if they are reached, they are removed from the HashMap<> idxDinBackward. It mains that are the remaining necessary backward propagation candidats.

The following (non animated) graphic should show this process. Note that the order is the order of the colors magenta, red, orange, green, cyan and blue. blue is the last backward propagation.

#### TODO image.

As result of this forward and backward propagation the most of pins in FBocks in the module, especially in expressions, are set to its fix data types whenever it is possible. If different fix data types are clashing in connections or depending pins, this is report as an error of propagation. It should be fixed in the module.

### 1.6.1.2 Forward and backward propagation of non dedicated pins

If pins remains which are not full dedicated in its data type, then the module itself is not full qualified. Code generation from only the module alone is not possible. The module can be used inside another module, and then this superior module should determine the data types of all to generate code.

But to can do so, the same instances of non full qualified **DType\_FBc1** is necessary on the inputs

or outputs of a module (favored: inputs) which are also used in the inner of the module, or just depending DType\_FBc1 are necessary to build as described in the following chapter for this module.

To do so, the same algorithm of propagation is done with the non full qualified module input and module output pins. As result, concise but not full qualified DType\_FBc1 instances are built with its Depenency

#### **1.6.1.3** Forward declaration for depending pins of a FBtype

If pins are not full qualified then the data type of some pins depends from another. If the data type of one pin is dedicated, also all or some other pins are then dedicated with the same data type. A simple expression can only have the same dedicated data type on all its pins expression relevant pins (except expr and THIS, see TODO chapter missing FBexpr presentation in Fbcl / IEC61499.

But specific mathematics expressions have depending dedications. Simple, look on the expression which combines real and imagine part to a complex value. It is drawn on top in the following image:

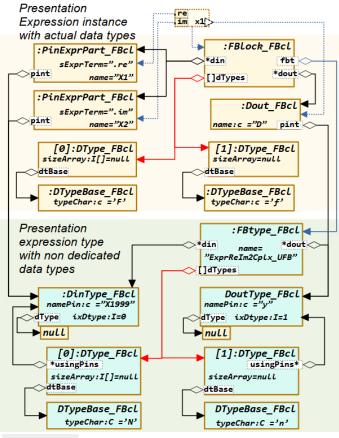

#### Figure 12:

OFB/ExprReIm2Cplx\_DTypeDep.png

Below there are some internal information about data associations as class diagram.

• The yellow part shows the presentation of the expression instance itself. The expression

is presented in the data model in Java by a fbcl/fblock/FBexpr FBcl (www) which is inherited fro FBlock FBcl, here shown. The FBlock FBcl refers the pins, shown as used types fbcl/fblock/PinExprPart FBcl (www), and Dout Fbc1, but derived from Pin FBc1, which contains the aggregation pint to the PinType Fbcl.

This aggregations go to the green part, which is the FBtype situation. The FBtype FBcl the instance with the is name "ExprReIm2Cplx UFB". It has independent from particular the usage the data pins (<u>ww</u>w) fbcl/fblock/DinType FBcl and fbcl/fblock/DoutType FBcl (www). Not shown here: Both are derived from **DinoutType FBc1**, and then from **PinType FBc1**. with its pins, which are here one **Dout FBc1** (a variable in generated code) and the both **Din FBc1** as inputs, derived to DinExpr\_Fbcl.

• The aggregation dType shown in the graphic is contained in the inherited class **DinoutType\_FBc1**. But for this type pins it is null, not set. Because the **data type is not dedicated**.

• Instead, the possible non dedicated data type(s) is/are referenced from the FBtype\_FBc1 in the array aggregation dTypes. That are the red aggregations. The both DinoutType\_Fbc1 objects contain the index in this aggregation array, and hence the aggregation via index ixDtype between the data pins and the data types of this pins.

• On creation of the ExprReIm2Clpx\_UFB instance first the corresponding dTypes aggregation array in <u>fbcl/fblock/FBlock\_FBcl</u> (www) remains empty, not determined in the FBlock itself, if a data type is not notated on this pins, as usual.

• But on data type propagation this instances are set from the real used data types. Then they are full dedicated for this using instance of the expression.

• The indices in Fblock\_FBc1#dTypes are determined by the indices <u>DinoutType FBcl.html#ixDtype</u>, as also the Dtype\_Fbcl instances there determines the kind of dependency between the both types. One is real, determined by 'N', the other is complex, determined by 'n', but both are depending. It means if one of the input is given as real type **float**, **typeChar 'F'**, then the output is dedicated by the correspond complex float type with **typeChar = 'f'**.

• And hence the input determines the output type, also if it is not the same, only depending, and the data type propagation can be forwarded from the outputs of the expression to the next FBlocks.

• The usingPins aggregation in Dtype\_FBc1 helps to find out the appropriate pins

## 1.6.2 Identification of the event flow due to data flow

In IEC61499 diagrams and language the **event flow** is an integral part of the model, planned by the architect of the solution. The *data flow* should match to the given event flow. Some special options are possible: Using data before they are newly calculated. It means that is a possibility, but also also a prone of error if mistakes are done.

In opposite, ordinary Function Block Diagrams uses only the *data flow* to calculate the

processing order paired with dedicated sample time designation.

For the UFBgl diagrams, the internal processing uses the event flow as in IEC61499, but it is not necessary to dedicate it in all details from the graphic model. It is automatically generated due to the data flow.

## 1.6.2.1 UFBgl: Binding event to data on in/outputs

Other than for reading for example Simulink diagrams, the UFBgl need a dedicated association between data in- and outputs and the associated event pins. With the given event

pins the data are related to the events, instead to *"sample times"*.

TODO adequate image as for simulink

### 1.6.2.2 Resulting evout because of evin of a FBlock

This is the question of track the event chain(s).

In chapter *Error: Reference source not found Error: Reference source not found* page Simple and Basic FBlocks are mentioned. Simple FBlocks have only one event input (evin) and one event output (evout) following the evin. Basic FBlocks can have more events. The special case of basic FBlocks with a simple regular state machine results in a non state-depending correlation between input and output events. This is regarded in building and executing the event chain. Such FBlocks are similar as classes (instances) of a class with more operations. The evin forces execution the operation, and on success the evout given with resulting data ready to get. But it is also similar to FBlocks in other Function Block Diagrams (such as Simulink) for each one sample time per event.

If a FBlock with a state machine is inside the module, it may build independent event outputs which builds an own event chain, as mentioned in the introduction to the chapter above.

### 1.6.2.3 Some Contemplation to bind data to events, event cluster

In Simulink events for that usage are unknown. Instead each data input should have a dedicated sample (step-) time association. The step time replaces the event association, if all functionality (all data pins of one step time) should be associated to one event flow. But this is also for optimization of code generation often not a good decision. It is better to have a fine division in primary independent function groups: For UFBgl and IEC61499 you can have this fine division by manually planning of data and event associations, whereby you have more events as step times. Lets look on an example:

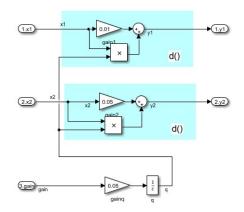

Figure 13: smlk/Testcg\_MdlTstepSmlk.png

All data have the same sample time here. But maybe it is not necessary to calculate the outputs of y2. Then it is better to have two event chains, one for y1 and a second for y2. A third event chain is given, because the q variable is a *"unit delay"*, a stored value from the sample time before calculated with the third event.

The associations of the din and dout with same sample times to different events is done with first back tracking from the data, detection which input data are necessary for one or a

#### **1.6.2.4** Info in pins for data to event processing

The Type <u>fblock.Evout\_FBcl</u> (<u>www</u>) contains two elements which are set temporary while built the event chain:

• Evinout\_FBcl#idxRepresentingEvents: This is a HashMap of <Evout\_Fbcl> which contains all events, which drives this event. This is essential to detect the situation which is shown in in the following chapter **1.6.3 OFB: Build** the event chain to prevent to much effort for unnecessary JOIN of events.

#### The fblock.Pin\_FBcl (www) contains

• Pin\_FBc1#mEvMd1Chain: Here the bit for the driving evinMd1 (possible more as one) are set, also on Din, Dout, Evin, Evout pins. This is used to prevent twice handling for the event chain built.

group of output data. Doing that also branches are detected: Some data should be calculated before, as common data for then independent branches. For that look to a more sophisticated example:

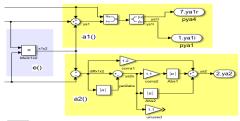

#### Figure 14: smlk/ParallelSimple\_smlk\_EvChainBack.png

Both yellow blocks a1) and a2) are independent and hence controlled by different event chains with own event inputs for the module. But to execute this blocks, it is necessary to calculate block e) before. This is the first event to call.

TODO more simple smlk model

TODO Test with UFBgl, manual drawn evin and also a manual EvJoin FBlock.

The <u>fblock.Evinout\_FBcl</u> (www) contains some elements which are set temporary while built the event chain:

• Evinout\_FBcl#mEvinClusterEnd: One bit for each evin in the module's inner evoutMdl array and in the array of inner evin for state corresponding machines. to the PinType Fbcl#ixPin. Any event pin of FBlocks is marked to designate the association to an event cluster per end event. This is used for backward event to data flow algorithm (currently in version 2024-03 not used, but it was used in 2019, todo: do not remove the idea).